## Ph.D. DISSERTATION

# Reconciling Low-Level Features of C with Compiler Optimizations

C의 저수준 기능과 컴파일러 최적화 조화시키기

BY

Jeehoon Kang

FEBRUARY 2019

DEPARTMENT OF ELECTRICAL ENGINEERING AND

COMPUTER SCIENCE

COLLEGE OF ENGINEERING

SEOUL NATIONAL UNIVERSITY

## Ph.D. DISSERTATION

# Reconciling Low-Level Features of C with Compiler Optimizations

C의 저수준 기능과 컴파일러 최적화 조화시키기

BY

Jeehoon Kang

FEBRUARY 2019

DEPARTMENT OF ELECTRICAL ENGINEERING AND

COMPUTER SCIENCE

COLLEGE OF ENGINEERING

SEOUL NATIONAL UNIVERSITY

## Reconciling Low-Level Features of C with Compiler Optimizations

C의 저수준 기능과 컴파일러 최적화 조화시키기

지도교수 허충길 이 논문을 공학박사 학위논문으로 제출함 2019 년 1 월

> 서울대학교 대학원 전기컴퓨터 공학부 강 지 훈

Jeehoon Kang의 공학박사 학위논문을 인준함

2019 년 1 월

| 위 원 장 |   | 이광근          |

|-------|---|--------------|

| 부위원장  |   | 허충길          |

| 위     | 원 | 전병곤          |

| 위     | 원 | 이재욱          |

| 위     | 원 | Derek Dreyer |

|       |   |              |

## **Abstract**

To improve the performance of C programs, mainstream compilers perform aggressive optimizations that may change the behaviors of programs that use low-level features in unidiomatic ways. Unfortunately, despite many years of research and industrial efforts, it has proven very difficult to adequately balance the conflicting criteria for low-level features and compiler optimizations in the design of the C programming language. On the one hand, C should support the common usage patterns of the low-level features in systems programming. On the other hand, C should also support the sophisticated and yet effective optimizations performed by mainstream compilers. None of the existing proposals for C semantics, however, sufficiently support low-level features and compiler optimizations at the same time.

In this dissertation, we resolve the conflict between some of the low-level features crucially used in systems programming and major compiler optimizations. Specifically, we develop the first formal semantics of relaxed-memory concurrency, separate compilation, and cast between integers and pointers that (1) supports their common usage patterns and reasoning principles for programmers, and (2) provably validates major compiler optimizations at the same time. To establish confidence in our formal semantics, we have formalized most of our key results in the Coq theorem prover, which automatically and rigorously checks the validity of the results.

**Keywords**: C, formal semantics, compiler verification, relaxed-memory concurrency, separate compilation, integer-pointer cast

Student Number: 2013-20737

The outcomes that matter in research are not numerous publications, best-paper awards, completed PhD theses, keynote invitations, software tools, citations and other measurable signs of progress. I was after real success, in the sense of changing the way the IT industry develops software. [...] By that standard, the story told in this article is one of glaring, unremitted and probably definitive failure.

—Bertrand Meyer [17]

## Acknowledgements

Without great sacrifices of teachers, I would not have been able to finish my Ph.D. Prof. Kwangkeun Yi bore with my childish enthusiasm and tamed it into a dedication. My advisor Prof. Chung-Kil Hur taught me how to read, write, listen, speak, and think by doing together. Dr. Derek Dreyer gave constructive advice that I can follow at just the right times. Now I realize everything they have done to me requires a lot of patience. I would like to say thank you with all my heart.

I would also like to thank Prof. Byung-Gon Chun and Prof. Jae W. Lee for reviewing and giving feedback on this dissertation and my job talk as committee members. I also thank William Mansky, Dmitri Garbuzov, Steve Zdancewic, Viktor Vafeiadis, Yoonseung Kim, and Ori Lahav for working together on the papers which this dissertation is based on, and thank Robbert Krebbers, Jim Apple, Xavier Leroy, Doug Lea, Alan Jeffrey, Andreas Lochbihler, James Riely, Peter Sewell, and Joe Tassarotti for very helpful feedback on the papers.

The papers on which this dissertation based are supported in part by the Engineering Research Center of Excellence Program of MSIP/NRF (Grant NRF-2008-0062609), the ICT R&D program of MSIP/IITP (Grant R0132-15-1006), Samsung Research Funding Center of Samsung Electronics (Project Number SRFC-IT1502-07), a Kwanjeong Educational Foundation Scholarship, and a Korea Foundation for Advanced Studies Scholarship.

I remember my friends. Jaeyeol have always been my teacher, mentor, friend, and brother, and he organized "Kang Sa Mo" for my wedding ceremony. Minsuk and Jonghwan took care of me as if I'm their younger brother. Hyeong Kyun and I went through bad times together as comrades, and Joonhyuk, Taehong, Hyunsung and I went through good times together as comrades. I remember Wonha. I also remember all ROPAS and

SF members, and especially Soonho, Wonchan, and Wontae for helping me in my early career.

None of this could have happened without my family. Mom and Dad, you have always provided me with all that I needed so far. Now I am starting to realize what it meant for you only after having my own child. All I can say is just thank you and love you. Grandma, you colored my childhood with joy and warmth. I miss you so much and I really hope you could attend my commencement ceremony. Minjung, your positive thinking helped us bond together as a family, in good times and in bad. You are probably the greatest sister in the history.

And Eunjung, my lovely and brilliant wife, you sacrificed a lot of things for this dissertation and my career. Thank you for supporting and loving me. This dissertation, as well as the rest of my life, is dedicated to you. Saeun, your smile raises me up even when I am totally exhausted. Someday you will grow up, but I will be your shelter forever. Eunjung and Saeun, I will always love you no matter what.

## **Contents**

| Abstract | :                         |                                                            | i   |

|----------|---------------------------|------------------------------------------------------------|-----|

| Acknow   | ledgeme                   | nts                                                        | iii |

| Chapter  | I Pr                      | cologue                                                    | 1   |

| 1        | Introdu                   | ction                                                      | 1   |

|          | 1.1                       | Conflict between Low-Level Features and Compiler Optimiza- |     |

|          |                           | tions                                                      | 4   |

|          | 1.2                       | Reconciling Low-Level Features with Compiler Optimizations | 7   |

| 2        | Backgro                   | ound: A Brief Tour of CompCert                             | 10  |

|          | 2.1                       | Compiler Correctness                                       | 11  |

|          | 2.2                       | Memory Model                                               | 13  |

|          | 2.3                       | The RTL Language                                           | 16  |

|          | 2.4                       | Constant Propagation                                       | 20  |

| Chapter  | II Re                     | elaxed-Memory Concurrency                                  | 26  |

| 3        | Introdu                   | ction                                                      | 26  |

|          | 3.1                       | Criteria for a Programming Language Memory Model           | 27  |

|          | 3.2                       | The "Out of Thin Air" Problem                              | 27  |

|          | 3.3                       | A "Promising" Semantics for Relaxed Memory                 | 29  |

| 4        | Basic M                   | Todel for Handling Relaxed Accesses                        | 30  |

|          | 4.1                       | Main Ideas                                                 | 31  |

|          | 4.2                       | Formal Definition                                          | 35  |

| 5        | Supporting Atomic Updates |                                                            | 37  |

| 6        | Full Mo                   | del                                                        | 40  |

|         | 6.1    | Release/Acquire Synchronization                     | 40 |

|---------|--------|-----------------------------------------------------|----|

|         | 6.2    | Sequentially Consistent (SC) Fences                 | 44 |

|         | 6.3    | "Plain" Non-Synchronizing Accesses                  | 45 |

|         | 6.4    | System Calls                                        | 46 |

|         | 6.5    | Modifying Existing Promises                         | 46 |

|         | 6.6    | Formal Model                                        | 47 |

| 7       | Result | s                                                   | 51 |

|         | 7.1    | Compiler Transformations                            | 51 |

|         | 7.2    | Compilation to TSO                                  | 53 |

|         | 7.3    | DRF Theorems                                        | 54 |

|         | 7.4    | An Invariant-Based Program Logic                    | 56 |

| 8       | Proofs | 8                                                   | 57 |

|         | 8.1    | Thread-Local Simulation Relation                    | 57 |

|         | 8.2    | Proof of DRF-RA                                     | 60 |

|         | 8.3    | Proof of DRF-LOCK                                   | 64 |

| 9       | Relate | d Work                                              | 66 |

| 10      | Follow | y-up and Future Work                                | 69 |

| Cl      |        | None and Committed to a small tent to a             |    |

| Chapter |        | Separate Compilation and Linking                    | 72 |

| 11      |        | uction                                              | 72 |

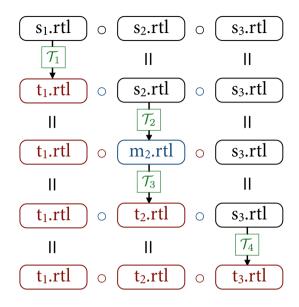

| 12      |        | iew                                                 | 75 |

|         | 12.1   | Compositional Correctness Level A                   | 75 |

|         | 12.2   | Compositional Correctness Level B                   | 77 |

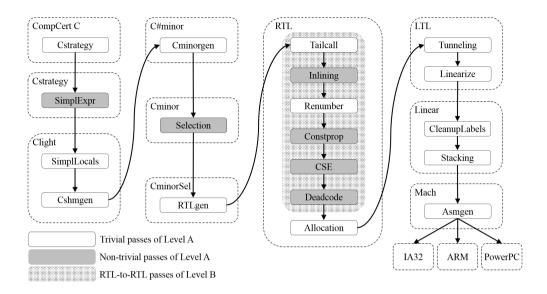

| 13      | -      | ing Constant Propagation to Separate Compilation    | 80 |

|         | 13.1   | Verifying Compositional Correctness Level A         | 80 |

|         | 13.2   | Verifying Compositional Correctness Level B         | 83 |

| 14      | -      | ing the Other Passes to Separate Compilation        | 84 |

|         | 14.1   | RTL-Level Optimizations that Rely on Value Analysis | 85 |

|         | 14.2   | Selection                                           | 85 |

|         | 14.3   | Inlining                                            | 87 |

|         | 14.4   | SimplExpr                                           | 87 |

| 15      |        | s                                                   | 87 |

| 16      |        | ssion                                               | 89 |

|         | 16.1   | Related Work                                        | 89 |

|         | 16.2   | Generality of Our Techniques                        | 92 |

|         | 16.3   | Impact                                              | 93 |

| Chapter   | IV     | Cast between Integers and Pointers         | 94  |

|-----------|--------|--------------------------------------------|-----|

| 17        | Intro  | duction                                    | 94  |

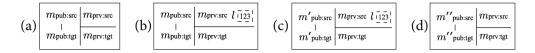

| 18        | Form   | nal Semantics of Hybrid Model              | 97  |

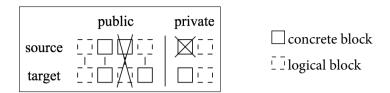

|           | 18.1   | Hybrid of Concrete and Logical Blocks      | 97  |

|           | 18.2   | Combining Logical and Concrete Blocks      | 97  |

|           | 18.3   | Choosing Concrete Blocks                   | 98  |

|           | 18.4   | Assigning Concrete Addresses               | 99  |

|           | 18.5   | Operations on Pointers                     | 100 |

|           | 18.6   | Dead Cast Elimination                      | 101 |

|           | 18.7   | Drawbacks of the Hybrid Model              | 102 |

|           | 18.8   | Language Semantics                         | 103 |

| 19        | Fix to | o the LLVM and GCC miscompilation Bugs     | 105 |

| 20        | Com    | piler Verification Techniques and Examples | 106 |

|           | 20.1   | Specification of Out of Memory             | 106 |

|           | 20.2   | Running Example & Informal Verification    | 107 |

|           | 20.3   | Memory Invariants                          | 109 |

|           | 20.4   | Proving Simulation                         | 111 |

|           | 20.5   | Examples                                   | 112 |

| 21        | Disci  | ussion                                     | 114 |

|           | 21.1   | Implementation and Experiment Details      | 114 |

|           | 21.2   | Related Work                               | 115 |

|           | 21.3   | Compatibility                              | 116 |

|           | 21.4   | Impact                                     | 118 |

| Chapter   | V      | Epilogue                                   | 119 |

| 22        | Conc   | clusion                                    | 119 |

| <b>초로</b> |        |                                            | 120 |

## **List of Figures**

| Figure I.1   | An LLVM bug in the presence of integer-pointer casts                           | 6   |

|--------------|--------------------------------------------------------------------------------|-----|

| Figure I.2   | RTL syntax                                                                     | 16  |

| Figure I.3   | RTL semantic domains                                                           | 17  |

| Figure I.4   | Operational semantics of RTL                                                   | 19  |

| Figure I.5   | Example of constant propagation                                                | 22  |

| Figure I.6   | $Comp Cert's \ simulation \ relation \ for \ the \ constant \ propagation \ .$ | 23  |

| Figure II.1  | Operational semantics for only relaxed read and write                          | 34  |

| Figure II.2  | Additional rule for updates                                                    | 40  |

| Figure II.3  | Full operational semantics                                                     | 49  |

| Figure II.4  | A simple derivation in the invariant-based program logic                       | 57  |

| Figure III.1 | Proving Level A correctness                                                    | 75  |

| Figure III.2 | Proving Level B correctness for RTL passes                                     | 78  |

| Figure III.3 | A bug due to CompCert 2.4 value analysis                                       | 82  |

| Figure III.4 | Classification of optimization passes in CompCert                              | 84  |

| Figure III.5 | Changes to lines of codes for LevelA and LevelB correctness .                  | 88  |

| Figure IV.1  | A GCC bug in the presence of integer-pointer casts                             | 95  |

| Figure IV.2  | Arithmetic optimization example I                                              | 98  |

| Figure IV.3  | Dead code elimination example                                                  | 99  |

| Figure IV.4  | Ownership transfer example                                                     | 100 |

| Figure IV.5  | Arithmetic optimization example II                                             | 101 |

| Figure IV.6  | Dead cast elimination example                                                  | 102 |

| Figure IV.7  | Memory invariants for the running example                                      | 108 |

| Figure IV.8  | Memory invariants for hybrid model                                             | 110 |

|              |                                                                                |     |

## Chapter I

## **Prologue**

#### 1 Introduction

The C programming language is the *lingua franca* for systems programming, mainly due to its three notable advantages: *low-level features*, *portability*, and *performance*. C provides low-level features that offer programmers precise control over hardware such as pointer manipulation, shared-memory concurrency, and asynchronous interrupt. At the same time, C is portable in that C programs can be compiled and then executed in most of the existing hardware. Furthermore, C provides decent performance: a program written in C are usually outperforming equivalent programs written in other languages—even including carefully hand-written assembly programs—when they perform exactly the same task. These advantages for decades have attracted system programmers, and as a result, a giant ecosystem was built around the C programming language.

C provides low-level features and portability—seemingly conflicting properties—at the same time because it is a balanced abstraction over various hardware assembly languages. If C were exposing too much detail of particular hardware architectures, then it would have not been able to support mismatching architectures, losing a significant degree of portability; on the other hand, if C were exposing too little detail of hardware architectures, then it would have not been able to provide low-level features. The design choice of C as a hardware abstraction is so popular that other systems programming

languages—such as C++, D, Objective C, Swift, and Rust—largely follow the design of C and are often called "C-like".

Compiler Optimizations Being a simple syntax translator from C to assembly languages, however, is insufficient for C compilers to provide the desired level of performance. Instead, compilers perform *optimizations* that transform the given program to be executed more efficiently in hardware while preserving its semantics. Optimizations are so effective that they have been an essential ingredient of compilers since the early days. For example, every system programmer expects a compiler to perform quite sophisticated optimizations such as register promotion [5] and register allocation [6]. Optimizations are becoming more important these days because recent hardware trends—such as SIMD, GPU, and accelerators—offer potential for compiler optimizations to further improve the performance of systems.

The following is an instance of the *constant propagation* optimization, which significantly improves the performance of compilation results and is thus performed by mainstream compilers such as GCC [2] and LLVM [3]:

Suppose g() is an external function whose body is unknown to the compiler, and print(a) prints the value of a to the screen. The function f() first assigns 42 to the local variable a (line 1), calls some unknown external function g() (line 2), and then prints a (line 3). As an optimization, mainstream compilers replace a with 42 at line 3, effectively propagating the constant 42 at line 1 to line 3. Compilers perform such an optimization even in the presence of a function call to the unknown function g(), because—at least in the viewpoint of compilers—the address of the variable a is not leaked to g() and thus its content cannot be modified by g().

This optimization, however, may change the program's behavior, putting the soundness of the optimization in danger. For instance, suppose that f() is linked with the

### following g():

```

void g() {

1: int anchor;

2: int *guess = &anchor + 10; // guessing &a

3: *guess = 666;

}

```

Here, the function g() tries to *guess* the address of a by exploiting the fact that stack usually grows downwards with a fixed offset: it first declares a variable anchor and guesses that a is located 10 words later than than anchor is. While extremely dangerous and thus discouraged, the guess sometimes happens to be correct, invalidating the compiler's reasoning that a is accessible only within the function f(). If it is the case, when linked with g(), the original f() will print the evil value 666; on the other hand, the optimized f() will print the expected value 42.<sup>1</sup>

To rescue the soundness of constant propagation, the ISO C18 standard [37] blames g() for violating the rule of the C programming language by marking it as invoking undefined behavior [37, §3.4.3p1]. Specifically, line 2 invokes undefined behavior because guess is derived from anchor and yet it does not point to the valid location within anchor's allocation [37, §6.5.6p8]. (Roughly speaking, all the pointers derived from anchor shall point to anchor; otherwise, the behavior is undefined.) Now an instance of undefined behavior allows compilers to do anything it chooses, from arbitrarily changing the code and thereby justifying the constant propagation optimization to even making "demons fly out of your nose" [8].<sup>2</sup>

Notice that C intentionally loses the ability to manipulate pointers in an unrestricted way—e.g., deriving the address of a from that of anchor—in order to justify the constant propagation optimization. This is beneficial because the performance improvement offered by compiler optimizations outweights the cost of the restriction on the low-level feature for unidiomatic programs. As a result, pointers in C should have a richer structure than those in assembly languages that have the same representation as integer values of the appropriate width and simply index into a single flat array representing memory.

$<sup>^1</sup>$ We got these results by separately compiling f() and g() and then linking them using GCC 8.2.1 with compile option -fno-stack-protector in an x86-64 machine running Linux 4.20.

<sup>&</sup>lt;sup>2</sup>Notice that undefined behavior is not necessary for higher-level languages—such as Java, C#, OCaml, Haskell—to justify compiler optimizations thanks to their lack of low-level features. For example, constant propagation is immediately justified in Haskell without resorting to undefined behavior thanks to its lack of raw pointer.

Such a practice of taming low-level features for supporting compiler optimizations is actually quite common in the design of the C programming language: mainstream compilers perform aggressive optimizations that may change the behaviors of programs that use low-level features in unidiomatic ways. As a result, C programs may have different meaning than the exactly same programs written in assembly languages (modulo syntactic differences). In other words, C is no longer just a thin wrapper around assembly languages but it should rather be an abstraction over both assembly languages *and* compiler optimizations.

### 1.1 Conflict between Low-Level Features and Compiler Optimizations

Unfortunately, despite many years of academic and industrial efforts [37], it has proven very difficult to adequately balance the conflicting criteria for low-level features and compiler optimizations in the design of the C programming language. On the one hand, C should support the common usage patterns of the low-level features in systems programming, such as relaxed-memory concurrency, separate compilation, and cast between integers and pointers. In addition, programmers should be able to reason about programs that use the low-level features. On the other hand, C should also support the sophisticated and yet effective optimizations performed by mainstream compilers, such as register promotion, constant propagation, and dead code elimination. To the best of our knowledge, none of the existing proposals for C semantics sufficiently support both low-level features and compiler optimizations at the same time.

**Prior Work** The ISO C standard, even after a series of revisions including C89, C99, C11, and C18, still has quite unclear specification for some of the low-level features as of this writing. First, ISO C18 [37] informally describes the C programming language in English prose, which is often ambiguous and confusing. The problem has only worsened by the fact that the description contains many ad-hoc exceptions including 203 cases of undefined behavior [37, J.2]. Second, ISO C18 intentionally leaves the precise meaning of some of the low-level features undefined. For example, the semantics of cast between integers and pointers is not properly defined in ISO C18, while it is essential for applications such as operating system kernels and language runtimes.

Accordingly, there have been numerous efforts to capture the subtleties of the ISO C standard by giving an alternative formal language definition [56, 83, 26, 63, 46]. However, all these projects—while supporting a significant subset of ISO C99 or LLVM IR—make unrealistic simplifying assumptions on C semantics and lack support for various low-level features.

As a result, many systems programming communities, *e.g.*, the Linux kernel developers, use their own *dialect* of C that is closer to assembly languages and supports more low-level features and less compiler optimizations than the standard. The dialects, however, are often informally described as the set of turned-on compiler optimizations (*e.g.*, "gcc -02"), whose meaning is unclear and unstable.

Problem The unresolved conflict between low-level features and compiler optimizations causes difficulties to both programmers and compiler writers. For programmers, it is difficult to expect how programs that use low-level features will behave because compilers may perform conflicting optimizations, which introduce surprising non-local changes and difficult-to-find bugs in program behavior [80, 81]. As a result, mainstream compilers are typically unused for safety-critical systems or used with only few compiler optimizations turned on, significantly increasing verification cost and degrading performance of safety-critical systems. One the other hand, for compiler writers, it is difficult to figure out whether an optimization is sound or not in the presence of low-level features. Even worse, sometimes a combination of optimizations—while each and every one of them seems legit—results in miscompilation bugs, for which it is unclear how to fix.

**A Miscompilation Bug** Figure I.1 presents an LLVM miscompilation bug<sup>3</sup> due to conflicting optimizations. Note that the type uintptr\_t is an integer type that is capable of holding a pointer value [37, \$7.20.1.4]. For this program, the expected outcome is either a=0 x=15 or a=100 x=0 for the following reasons:

- Suppose n=0. Then pi points to x after line 12. Thus line 13 writes 15 to x, and the end result is a=0 x=15.

- Suppose otherwise. Then a=100 and pi points to y after line 12. Thus line 13 writes 15 to y, and the end result is  $a=100 \times 0$ .

However, the result a=0 x=0 is observed when c.c and b.c are compiled with clang -02 and then executed due to the following series of optimizations:

1. The integer comparison pi != yi at line 4 is replaced with the pointer comparison &x != y+1.

$<sup>^3</sup>$ This bug is reported in the LLVM bug tracker: https://bugs.llvm.org/show\_bug.cgi?id= 34548

```

// c.c

#include <stdio.h>

#include <stdint.h>

void f(int*, int*);

int main()

1: int a=0, y[1], x = 0;

2: uintptr_t pi = (uintptr_t) &x;

3: uintptr_t yi = (uintptr_t) (y+1);

4: uintptr_t n = pi != yi;

5: if (n) {

6: a = 100;

7:

pi = yi;

8: }

9: if (n) {

10: a = 100;

11:

pi = (uintptr_t) y;

12: }

13: *(int *)pi = 15;

14: printf("a=%d x=%d\n", a, x); // observed: a=0 x=0

15: f(\&x,y);

16: return 0;

}

// b.c

void f(int*x, int*y) {}

```

Figure I.1 An LLVM bug in the presence of integer-pointer casts

- 2. The compiler assumes n=0, which is allowed since now line 4 is comparing pointers from different origins.

- 3. Lines 5-12 is eliminated since the condition n evaluates to false.

- 4. (int\*)pi at line 13 is replaced with (int\*)yi since n=0, and then with y+1

since yi=(uintptr\_t)(y+1).

- 5. Line 13 is eliminated since it is writing to an invalid address y+1. Then line 14 prints a=0 x=0.

In short, LLVM has a miscompilation bug due to the conflict among the above five optimizations. However, each of them looks legit—at least in the viewpoint of the LLVM compiler—and it is unclear which one(s) is to blame. That is one of the reasons this bug is still open in the bug tracker as of this writing.

#### 1.2 Reconciling Low-Level Features with Compiler Optimizations

In this dissertation, we resolve the conflict between some of the low-level features crucially used in systems programming and major compiler optimizations. Specifically, we develop formal semantics of relaxed-memory concurrency (Chapter II), separate compilation (Chapter III), and cast between integers and pointers (Chapter IV) that (1) supports their common usage patterns and reasoning principles, and (2) provably validates major compiler optimizations at the same time.

Our formal semantics is beneficial to both programmers and compiler writers. Since formal semantics is a mathematically clear definition of program behaviors, it makes possible for programmers to expect how compiled programs will behave regardless of which optimizations are performed by compilers. On the other hand, compiler writers can figure out whether an optimization is sound or not using formal semantics as the criteria. In particular, with formal semantics, we can point out which optimization(s) is to blame in the miscompilation bug above.

To establish confidence in our formal semantics, we prove the soundness of compiler optimizations in the presence of the low-level features. The soundness proof guarantees that they preserve the semantics of source programs and do not introduce any bugs. The absence of miscompilation bugs ensures higher level of reliability and thus enables optimizations to be used even for safety-critical systems with confidence. We have formalized all the soundness proofs reported in this dissertation in the Coq theorem prover [35], which automatically and rigorously checks the validity of the soundness proofs. The formalization is available online [1].

In the rest of this section, we will briefly describe our main contributions, namely developing formal semantics of three low-level features of C.

Chapter II: Relaxed-Memory Concurrency Relaxed-memory concurrency is the study of *relaxed behaviors*, which are observable behaviors of concurrent programs beyond those allowed in *sequential consistency* (think: interleaving of the executions of threads). Relaxed behaviors are made possible due to hardware and compiler optimizations such as out-of-order execution or instruction reordering/merging. While relaxed behaviors complicate reasoning of concurrent programs, they are unavoidable in effectively exploiting the parallelism provided by shared-memory architecture. Despite many years of research, however, it has proven very difficult to develop a formal semantics for programming languages with relaxed-memory concurrency that adequately balances the conflicting desiderata of programmers and compilers.

In this chapter, we propose the first formal semantics of relaxed-memory concurrency that (1) justifies simple invariant-based reasoning, thus demonstrating the absence of bad "out-of-thin-air" behaviors, (2) supports "DRF" guarantees, ensuring that programmers who use sufficient synchronization need not understand the full complexities of relaxed-memory semantics, (3) is implementable, in the sense that it provably validates many standard compiler optimizations and reorderings, as well as standard compilation schemes to x86-TSO, (4) accounts for a broad spectrum of low-level concurrency features in C, and (5) defines the semantics of racy programs without relying on undefined behaviors, which is a prerequisite for applicability to type-safe languages like Java. The key novel idea behind our semantics is the notion of promises: a thread may make the effect of a write before actually executing it, thus enabling other threads to read from that write out of order. Crucially, to prevent out-of-thin-air behaviors, a promise step requires a thread-local certification that it will be possible to execute the promised write even in the absence of the promise.

Our semantics draws interest from both industry and academia. Our semantics not only serves as a guide to C/C++ relaxed-memory concurrency [7, 4] but also influences the discussion on the standard semantics for C/C++ and compiler IRs (private communication in mailing lists). Svendsen *et. al.* developed reasoning principles for our semantics [77], and Podkopaev *et. al.* validated compilation schemes for our semantics to various architectures such as ARMv7, ARMv8, RISC-V, and Power [68]. Furthermore, the idea of promises and certification is also used to model the relaxed-memory concurrency in ARMv8 and RISC-V [70].

This chapter draws heavily on the work and writing in the following paper:

[40] **Jeehoon Kang**, Chung-Kil Hur, Ori Lahav, Viktor Vafeiadis, Derek Dreyer. *A Promising Semantics for Relaxed-Memory Concurrency*. **POPL 2017**.

Chapter III: Separate Compilation and Linking Separate compilation and linking is essential in practice because they significantly reduces compilation time. However, major compiler verification efforts, such as CompCert and Vellvm, have traditionally simplified the verification problem by restricting attention to the correctness of whole-program compilation, leaving open the question of how to verify the correctness of separate compilation. Recently, a number of sophisticated techniques have been proposed for proving more flexible, compositional notions of compiler correctness, but these approaches tend to be quite heavyweight compared to the simple "closed simulations" used in verifying whole-program compilation. Applying such techniques to a compiler like CompCert, as Stewart *et. al.* have done [76], involves major changes and extensions to its original verification.

In this chapter, we show that if we aim somewhat lower—to prove correctness of separate compilation, but only for a single compiler—we can drastically simplify the proof effort. Toward this end, we develop several lightweight techniques that recast the compositional verification problem in terms of whole-program compilation, as far as the compiler's transformations and optimizations satisfy what we call *monotonicity*. The proof techniques enable us to largely reuse the closed-simulation proofs from existing compiler verifications.

We demonstrate the effectiveness of these techniques by applying them to Comp-Cert 2.4, converting its verification of whole-program compilation into a verification of separate compilation in less than two person-months. This conversion only required a small number of changes to the original proofs. Along the way, we uncovered two compiler bugs—one of which is on separate compilation and the other is orthogonal to separate compilation—and our proof techniques are subsequently adopted in Comp-Cert 2.7.

This chapter draws heavily on the work and writing in the following paper: [42] **Jeehoon Kang**, Yoonseung Kim, Chung-Kil Hur, Derek Dreyer, Viktor Vafeiadis. *Lightweight Verification of Separate Compilation*. **POPL 2016**.

**Chapter IV: Cast between Integers and Pointers** Cast between integers and pointers is one of the defining characteristic of the C programming language in that it allow cross-platform low-level manipulation of memory layout, which is essential for applications such as operating system kernels and language runtimes. However, the feature

drastically conflicts with major compiler optimizations, as demonstrated by the example shown in Figure I.1. The ISO C standards try to reconcile the feature and the optimizations using the notion of *provenance*, but it fails to support certain common optimizations and requires an intrusive change to the language semantics.

In this chapter, we propose the first formal semantics of cast between integers and pointers that (1) fully supports operations on the representation of pointers, including all arithmetic operations for pointers that have been cast to integers, (2) validates major compiler optimizations on memory accesses, and (3) is simple to understand and program with. The key novel idea behind our semantics is the notion of *concretization*: when allocated, a memory block is not assigned a concrete address yet; only when it is required by a pointer-to-integer cast, the block is lazily assigned a concrete address, *i.e.*, the block is concretized.

Along the way, we discovered a GCC bug in the presence of integer-pointer casts, which clearly shows it is safe to turn off too aggressive alias analyses. Furthermore, our idea has subsequently been refined by follow-up papers by other researchers [54, 60], which are accompanied with promising revision proposals to the LLVM IR and the ISO C standard.

This chapter draws heavily on the work and writing in the following paper: [41] **Jeehoon Kang**, Chung-Kil Hur, William Mansky, Dmitri Garbuzov, Steve Zdancewic, Viktor Vafeiadis. *A Formal C Memory Model Supporting Integer-Pointer Casts.* **PLDI 2015**.

**Organization** The rest of this chapter provides the technical background on formal semantics and compiler verification that informs the rest of this dissertation (Section 2). Chapters II to IV present the main contributions of this dissertation. This dissertation concludes with Chapter V, which summarizes its contributions, impacts, and future work (Section 22).

## 2 Background: A Brief Tour of CompCert

Before delving into the main contributions, we briefly review the technical background on formal semantics and compiler verification that informs the rest of this dissertation, using the CompCert C compiler [55] as the learning material. The technical ideas and results presented in this section apply not only to CompCert but also to other formal semantics and compiler verification projects as well.

The CompCert project was initiated by Xavier Leroy over ten years ago and then grows as the first realistic verified compiler. CompCert is verified in the sense that it "is accompanied by a machine-checked proof of a semantic preservation property: the

generated machine code behaves as prescribed by the semantics of the source program." As such, CompCert guarantees that program analyses and verifications performed on its input carry over soundly to its machine-level output. CompCert is realistic in the sense that it "could realistically be used in the context of production of critical software". It compiles a significant subset of ISO C99 down to several architectures, and it performs a number of common and useful optimizations. It received significant interest from the avionics industry [14, 75], and recently, it is certified for being used for nuclear power plant [50]. It has also served as a fundamental building block in academic work on end-to-end verified software [12].

In this section, we first explain CompCert's correctness statement, as well as its simulation verification technique (Section 2.1). To flesh out the details on formal semantics and compiler verification, we use RTL—one of CompCert's internal representations—and constant propagation—one of CompCert's optimizations—as a running example. Specifically, We first review CompCert's memory model that is specifically designed to verify compiler optimizations (Section 2.2). Then we explain the RTL language on which constant propagation and most of the other optimizations are performed in the CompCert's compilation pipeline (Section 2.3), and how constant propagation works and how CompCert verifies it (Section 2.4). Throughout this section, we keep the presentation semi-formal, abstracting away unnecessary detail to get across the main ideas. For more details, we refer the reader to [55, 57].

### 2.1 Compiler Correctness

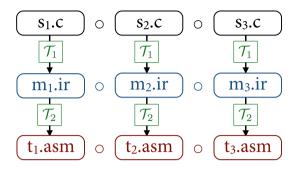

**End-to-End Correctness** Roughly speaking, the correctness result of CompCert can be understood to assert *semantic preservation*, which in turn means the following. Suppose s.c is a "source" file (in C), t.asm is a "target" file (in assembly), and  $\mathcal C$  is a verified compiler (represented as a function from C files to assembly files).

$$\frac{\mathcal{C}(\texttt{s.c}) = \texttt{t.asm} \qquad s = load(\texttt{s.c}) \qquad t = load(\texttt{t.asm})}{Behav(s) \supseteq Behav(t)}$$

If t.asm is the result of compiling s.c with  $\mathcal{C}$ , then executing t.asm according to assembly semantics will result in a subset of the behaviors one could observe from executing s.c according to C semantics. (We write s = load(s.c) to denote the *machine state* that results from loading s.c into memory, Behav(s) to denote the observable behaviors of the execution of s, and analogously for t and t.asm.) Hence, we say that t.asm, the target-level output of  $\mathcal{C}$ , refines its source-level input, s.c.

Notice that the compiler correctness statement presented here will be generalized to support separate compilation in Chapter III.

**Set of Behaviors** We consider sets of behaviors as opposed to single behaviors because a program may produce multiple behaviors due to nondeterminism. Given a set of I/O events that programs may generate and users may observe, a behavior is one of the following three forms: (1) a terminating execution producing a finite sequence of I/O events,  $e_1, \dots, e_n$ , term; (2) a diverging execution that has produced only a finite sequence of I/O events,  $e_1, \dots, e_n$ , nonterm; and (3) a diverging execution producing an infinite sequence of I/O events,  $e_1, \dots, e_n, \dots$ .

Undefined behavior requires special attention in defining the set of behaviors, because the program states in the condition are neither terminated nor transitioning to other states, fitting into none of the behavioral categories. We assign *the set of all behaviors* to the program states invoking undefined behavior in order to validate compiler optimizations: if the source program's behavior is undefined, then compiler can choose any program as its result; on the other hand, if the target program's behavior is undefined, then the source program's behavior should also be undefined.

Notice that the notion of behaviors presented here will be generalized to support out-of-memory in Chapter IV.

**Per-Pass Correctness** To verify compilation correctness for the compiler C, Comp-Cert verifies each pass of C independently. Specifically, for each pass (transformation) T from language  $L_1$  to  $L_2$ —where the  $L_i$ 's may be C, assembly, or some intermediate languages—we show the following:

$$\frac{\mathcal{T}(\texttt{s.11}) = \texttt{t.12} \qquad s = load(\texttt{s.11}) \qquad t = load(\texttt{t.12})}{Behav(s) \supseteq Behav(t)}$$

That is, given the input s.l1 and output t.l2 of the  $\mathcal{T}$  transformation, we show that the behaviors of t.l2 are contained within those of s.l1. Since subset inclusion is transitive, it easy to see that the proofs of the constituent passes of  $\mathcal{C}$  compose to establish the correctness of  $\mathcal{C}$  as a whole.

**Verifying Per-Pass Correctness** Now how does one actually prove the verification condition for each individual pass? The standard approach taken by CompCert is to use (closed) simulations. Informally, we will say that a *simulation* R is a relation between running programs (*i.e.*, machine states) in  $L_1$  and  $L_2$  such that, if  $(s, t) \in R$ , then the behaviors one observes while stepping through the execution of t are matched by corresponding observable behaviors in the execution of t. One can think of t as imposing an invariant, which describes (and connects) the possible machine states of the source and target programs, and which must be maintained as the programs execute.

We leave further details about simulations until Section 2.4; suffice it to say that they satisfy the following "adequacy" property:

$$\frac{R \text{ is a simulation} \qquad (s,t) \in R}{\text{Behav}(s) \supseteq \text{Behav}(t)}$$

Thus, to establish the verification condition for pass  $\mathcal{T}$ , it suffices to exhibit a simulation R that relates load(s.11) and load(t.12).

In the rest of this section, we flesh out the details on formal semantics and compiler verification in CompCert, using constant propagation as the running example. Constant propagation is essentially a transformation that optimizes memory operations, so we will first review their semantics in CompCert.

### 2.2 Memory Model

CompCert supports the following memory operations:

```

\begin{aligned} &load \in \mathsf{Mem} \to \mathsf{Addr} \to \mathbb{P}(\mathsf{Val}) \\ &store \in \mathsf{Mem} \to \mathsf{Addr} \to \mathsf{Val} \to \mathbb{P}(\mathsf{Mem}) \\ &malloc \in \mathsf{Mem} \to \mathsf{uint32} \to \mathbb{P}(\mathsf{Addr} \times \mathsf{Mem}) \\ &free \in \mathsf{Mem} \to \mathsf{Addr} \to \mathbb{P}(\mathsf{Mem}) \end{aligned}

```

Memory,  $m \in \text{Mem}$ , supports four operations: load, store, malloc, and free. Note that all operations may produce multiple results due to the nondeterminism arising from e.g., concurrency. A load operation reads the value,  $v \in \text{Val}$ , of an address,  $a \in \text{Addr}$ , and a store operation writes a value to an address in the memory. If a load or store operation access an illegal address, then there are no valid results. A malloc operation allocates a memory object of the specified size of type uint32 (the set of 32-bit unsigned integers), returning the new memory and the address of the allocated object, and a free operation deallocates an allocated memory object.

Now we define the semantic domain for and the semantics of those memory operations, or in other words, define the *memory model*. The memory model presented here will be generalized to support integer-pointer casts and relaxed-memory concurrency in Chapter IV and Chapter II, respectively.

To simplify the presentation, we do not discuss many aspects of C memory models that are orthogonal to the contributions of this dissertation. Specifically, we (1) assume a 32-bit architecture: words are 4 bytes wide and the size of the address space is  $2^{32}$ , as eminent from the signature of *malloc*; (2) consider only unsigned integer and pointer

values, and omit values of other types such as int32, float or char; and (3) omit subword arithmetic, and assume each address stores a 32-bit value.

**Concrete Model** The most straightforward way to define a memory model is closely following the assembly language: pointers have the same representation as integer values of the appropriate width, and they simply index into a single flat array representing memory. In such a *concrete memory model*, memory consists of a  $2^{32}$ -sized array of values, and a list of allocated blocks, represented as pairs (p, n) of the block's starting address and its size. Loading from or storing to an unallocated address raises an error (*i.e.*, undefined behavior). Values are just 32-bit integers, since pointers are merely integers in the concrete model.

Mem

$$\stackrel{\text{def}}{=}$$

(uint32  $\rightarrow$  Val)  $\times$  1ist Alloc Alloc  $\stackrel{\text{def}}{=}$  {  $(p, n) \mid p \in \text{uint32} \land n \in \text{uint32}$  } Val  $\stackrel{\text{def}}{=}$  {  $i \in \text{uint32}$  }

Memory allocation inserts a block into the list of allocated blocks, whereas deallocation removes one. Overall, the list of allocated blocks should be *consistent*:<sup>4</sup>

- If (p, n) is allocated, then  $\emptyset \neq [p, p + n) \subseteq (0, 2^{3^2} 1)$ .

- If blocks  $(p_1, n_1)$  and  $(p_2, n_2)$  are distinct allocations, their ranges  $[p_1, p_1 + n_1)$  and  $[p_2, p_2 + n_2)$  are disjoint.

The concrete model, however, *does not support standard compiler optimizations*. As we have seen in Section 3, constant propagation is unsound on the concrete model in the presence of external function calls, because the model does not provide a mechanism for ensuring that a module has exclusive control over some part of memory, and as a result, programmers should pessimistically assume that unknown code can read and update the contents of every allocated memory cell. Furthermore, dead allocation elimination is also unsound in the concrete model. For example, the following transformation—removing the unused local variable a—might change the behavior of the program: by virtue of there being one fewer memory cells allocated, the call to g() might succeed

<sup>&</sup>lt;sup>4</sup>These are a subset of malloc's properties according to the ISO C<sub>18</sub> standard. For more details, see [37, §7.22.3p1 and §6.5.8p5].

where initially it exhausted memory:

CompCert's Logical Model In order to support standard compiler optimizations, CompCert is based on a *logical* memory model [56, 57] rather than the naive concrete model. In the logical model, memory is a finite collection of logical blocks with unique block identifiers, together with the maximum of the allocated block identifiers. Each block is a contiguous, fixed-sized array of values annotated with a validity flag v that indicates whether the block is accessible or has been freed. As before, accessing a freed block raises an error. Values are either 32-bit integers, logical addresses, or the special *undefined value* that represents uninitialized data. Here, a logical address (l, i) consists of a block identifier l and an offset i inside the block.

```

\begin{aligned} & \operatorname{Mem} \ \stackrel{\mathrm{def}}{=} \big\{ \ (nb,bs) \ | \ nb \in \operatorname{BlockId} \wedge bs \in \operatorname{BlockId} \rightharpoonup_{\operatorname{fin}} \operatorname{Block} \big\} \\ & \operatorname{Block} \ \stackrel{\mathrm{def}}{=} \big\{ \ (v,n,c) \ | \ v \in \{\operatorname{valid}, \operatorname{freed}\} \wedge n \in \mathbb{N} \wedge c \in \operatorname{Val}^n \big\} \\ & \operatorname{Val} \ \stackrel{\mathrm{def}}{=} \big\{ \ i \in \operatorname{uint32} \big\} \uplus \operatorname{Addr} \uplus \big\{ \operatorname{undef} \big\} \\ & \operatorname{Addr} \ \stackrel{\mathrm{def}}{=} \big\{ \ (l,i) \in \operatorname{BlockId} \times \operatorname{uint32} \big\} \end{aligned}

```

An important advantage of the logical model over the concrete one is that it *allows* functions to have exclusive control over a logical block as long as they do not allow its address to escape. The reason is that it is not possible to manufacture the logical address of an already allocated block. This property guarantees the correctness of many useful optimizations, such as constant propagation across function calls and dead allocation elimination. A secondary advantage is that programs have *infinite memory*, rendering their allocation behavior unobservable, which in turn makes it easy for compilers to remove dead allocations.

Apart from that logical models have a slightly more complicated semantics, their main disadvantage is that *they do not support integer-to-pointer casts* very well. As a result, CompCert does not support real-world use cases of integer-pointer casts well. Specifically, they are treated as nops (*i.e.*, the identity function), and thus variables of integer (or pointer) types can contain both integers and logical addresses. This conflicts with the intention of integer-pointer casts to freely manipulated pointers as if they are integer values. We will address this disadvantage in Chapter IV.

```

Prog := \overline{Decl}

Decl := extern [const] Id[uint32]

// External Variable

\lceil \text{const} \rceil \text{Id}[\text{uint32}] := \{ \overline{\text{GVal}} \}

// Variable

extern Id FSig

// External Function

Id FDef

// Function

FSig ::= (\overline{Reg})

// Function Signature

FDef ::= (\overline{Reg}) { \overline{Reg}; sp[uint32]; Code } // Function Definition

Code := \overline{NodeId : Instr}

Instr ::= Reg := FVal

jmp NodeId

// Immediate Value

Reg := op \overline{Reg}

jmp NodeId

// Operation

Reg := FVal[uint32] jmp NodeId

// Load

FVal[uint32] := Reg jmp NodeId

// Store

cond-op Reg? jmp NodeId: jmp NodeId

// Conditional

Reg := FVal(\overline{Reg})

jmp NodeId

// Call

return Reg

// Return

GVal

::= Id | uint32 | undef

FVal

∷= GVal | Reg | sp

uint32 ::= the set of 32-bit unsigned integers

::= the set of identifiers for variables and functions

Id

Reg

::= the set of register names

NodeId ::= the set of node labels

```

Figure I.2 RTL syntax

It is worth noting that the logical model is not intended to replace the memory model in the ISO C18 standard. It is a formal refinement of the (informal) standard that can be used for formally reasoning about programs and program transformations (as in compiler verification).

#### 2.3 The RTL Language

So far we discussed CompCert's logical memory model and its advantages. To provide a more concrete context for formal semantics and compiler verification, we explain the syntax and semantics of CompCert's register transfer language (RTL), the compiler's internal language where most of its optimizations take place. For presentation purposes, we simplify the language a bit by removing types and other unnecessary details.

```

\begin{aligned} \operatorname{GEnv} & \stackrel{\operatorname{def}}{=} \left\{ \left( g, d \right) \mid g \in \operatorname{Id} \rightharpoonup_{\operatorname{fin}} \operatorname{BlockId} \land \\ & d \in \operatorname{BlockId} \rightharpoonup_{\operatorname{fin}} \operatorname{FSig} \uplus \operatorname{FDef} \right\} \\ \operatorname{State} & \stackrel{\operatorname{def}}{=} \operatorname{IState} \uplus \operatorname{CState} \uplus \operatorname{RState} \\ \operatorname{IState} & \stackrel{\operatorname{def}}{=} \left\{ \operatorname{ist} m \, s \, fd \, sp \, \underline{pc \, rs} \mid \\ & m \in \operatorname{Mem} \land s \in \operatorname{\overline{StkFrm}} \land fd \in \operatorname{FDef} \land \\ & sp \in \operatorname{Addr} \land pc \in \operatorname{NodeId} \land rs \in \operatorname{Reg} \rightharpoonup_{\operatorname{fin}} \operatorname{Val} \right\} \\ \operatorname{CState} & \stackrel{\operatorname{def}}{=} \left\{ \operatorname{cst} m \, s \, fds \, vs \mid m \in \operatorname{Mem} \land s \in \operatorname{\overline{StkFrm}} \land \\ & fds \in \operatorname{FDef} \uplus \operatorname{FSig} \land vs \in \operatorname{\overline{Val}} \right\} \\ \operatorname{RState} & \stackrel{\operatorname{def}}{=} \left\{ \operatorname{rst} m \, s \, v \mid m \in \operatorname{Mem} \land s \in \operatorname{\overline{StkFrm}} \land v \in \operatorname{Val} \right\} \\ \operatorname{StkFrm} & \stackrel{\operatorname{def}}{=} \left\{ (r, fd, sp, pc, rs) \mid r \in \operatorname{Reg} \land fd \in \operatorname{FDef} \land \\ & sp \in \operatorname{Addr} \land pc \in \operatorname{NodeId} \land rs \in \operatorname{Reg} \rightharpoonup_{\operatorname{fin}} \operatorname{Val} \right\} \end{aligned}

```

Figure I.3 RTL semantic domains

**Syntax** The syntax of the CompCert's RTL is given in Figure I.2. Programs are just a list of global declarations, which consist of (1) declarations of external variables and functions provided by different compilation units, and (2) definitions of variables and functions provided by the current compilation unit. For global variable declarations and definitions, we also specify a (non-negative) integer number denoting the size of the declared block in bytes.

Function declarations only contain the function signature, which is a list of parameters, but function definitions additionally contain a list of local registers, the size of their stack frame, and the code. The code is essentially a control-flow graph of three-address code: it is represented as a mapping from node identifiers to instructions, where instructions either do some local computation (*e.g.*, write a constant to a register, or perform some arithmetic computation), load from a memory address, store to memory, do a comparison, call a function, or exit the function and return a result. Each instruction also stores the node identifier(s) of its successor instruction(s).

Throughout we assume that programs satisfy some basic well-formedness properties: there cannot be multiple definitions for the same global variable, declarations and definitions of the same variable should have matching signatures, and the parameter and local variable lists for each function do not have duplicate entries.

**Semantics** The semantic domain used in CompCert's RTL is given in Figure I.3. A global environment,  $ge = (g, d) \in GEnv$ , maps each global variable name to a

logical block identifier, and each logical block identifier corresponding to some function's code to either the corresponding function signature for external functions or the corresponding function definition for functions defined in the program.

Program states can be of three kinds: normal instruction states (ist), call states (cst) just before passing control to an invoked function, and return states (rst), just after returning from an invoked function. Instruction states store the memory (m), the sequence of parent stack frames (s), the definition of the function whose body is currently executed (fd), the current stack pointer (sp), the program counter (pc), and the contents of the local registers (rs). Call states record the memory, the stack, and the function to be called (fds) with its arguments (args). The function to be called can be either an internal function, in which case we record its definition, or an external one, in which case we record its signature. Return states record just the memory, the stack, and the value that was returned by the function. A stack s is a list of stack frames, each of which records the same information as normal instruction states, except with the addition of a register name r where its return value should be stored, and minus the memory (m) and stack (s) components.

The meaning of programs is described by three definitions:

```

get\text{-}genv \in \operatorname{Prog} \to \operatorname{GEnv}

load \in \operatorname{Prog} \to \operatorname{State}

\leftrightarrow \in \mathbb{P}(\operatorname{GEnv} \times \operatorname{State} \times \operatorname{Event} \times \operatorname{State})

```

The first function, get-genv(prg), returns the global environment corresponding to the program: it "allocates" the global variables of the program sequentially in blocks 1, 2, 3, and so on, and maps the blocks corresponding to function symbols to the relevant function definition or signature. Similarly, load(prg) returns the initial state obtained by loading a program into memory: it initializes the memory m with the initial values of the global variables at the appropriate addresses generated by get-genv(prg), and returns a call state, cstm[]fd[], where fd is the function definition corresponding to main(). Loading is a partial function because it is undefined for programs without a main() function.

The  $\hookrightarrow$  relation is a small-step reduction relation describing how program states evolve during the computation. For clarity, we write  $s \stackrel{\sigma}{\hookrightarrow}_{ge} s'$  instead of  $(ge, s, \sigma, s') \in \hookrightarrow$ . The operational semantics for RTL is fairly standard and shown in Figure I.4: there is a rule for each of the various basic instructions of the language. Starting from normal instruction states, the instruction at the node pointed to by the program counter is scrutinized (fd@pc). Depending on what instruction is there, only one rule is applicable.

```

(IMM)

(OP)

fd@pc = (dst := op \ args \ jmp \ pc')

rs' = rs[dst \leftarrow \llbracket op \rrbracket (ge, sp, \llbracket args \rrbracket (rs))]

fd@pc = (dst := src jmp pc')

rs' = rs[dst \leftarrow [src] (ge, sp, rs)]

ist m s fd sp pc rs \stackrel{\epsilon}{\hookrightarrow}_{g_{\ell}} ist m s fd sp pc' rs'

ist m s fd sp pc rs \stackrel{\epsilon}{\hookrightarrow}_{qe} ist m s fd sp pc' rs'

(LOAD)

(STORE)

fd@pc = (dst := src[n] jmp pc')

fd@pc = (dst[n] := src jmp pc')

(l,i) = \llbracket src \rrbracket (ge, sp, rs)

(l,i) = [dst](ge,sp,rs)

rs' = rs[dst \leftarrow m[(l, i + n)]]

m' = m[(l, i+n) \leftarrow [src](rs)]

ist m s fd sp pc rs \xrightarrow{\epsilon}_{ge} ist m s fd sp pc' rs'

ist m s fd sp pc rs \xrightarrow{\epsilon}_{\sigma_{\ell}} ist m' s fd sp pc' rs

(COND)

fd@pc = (cond-op \ args ? jmp \ pc_1 : jmp \ pc_2)

b = [[cond-op]](ge, sp, [[args]](rs))

pc' = b? pc_1 : pc_2

ist m s fd sp pc rs \stackrel{\epsilon}{\hookrightarrow}_{ge} ist m s fd sp pc' rs

(CALL1)

fd@pc = (res := f(args) \text{ jmp } pc')

(l,o) = [\![f]\!] (ge, sp, rs)

fds' = findfunc(ge, l)

vs = [args](rs)

ist m s f d s p p c r s \stackrel{\epsilon}{\hookrightarrow}_{g e} cst m ((res, f d, s p, p c', r s) :: s) f d s' v s

(CALL2-INTERNAL)

(m', l) = alloc(m, stacksize(fd))

(CALL2-EXTERNAL)

pc = \text{entrynode}(fd)

(\sigma, v, m') \in \text{extcall-sem}(fs, ge, vs, m)

rs = init-regs(params(fd), vs)

cst m s f s v s \stackrel{\sigma}{\hookrightarrow}_{ge} r s t m' s v

cst m s f d v s \stackrel{\epsilon}{\hookrightarrow}_{ge} ist m' s f d(l, o) p c r s

(RETURN1)

fd@pc = (return r)

v = \llbracket r \rrbracket (rs)

(RETURN2)

rs' = rs[res \leftarrow v]

m' = free(m, sp, stacksize(fd))

rst m (res, fd, sp, pc, rs)::s v \stackrel{\varepsilon}{\hookrightarrow}_{ge} ist m s fd sp pc rs'

ist m s fd sp pc rs \stackrel{\epsilon}{\hookrightarrow}_{ge} rst m' s v

```

Figure I.4 Operational semantics of RTL

The corresponding rule calculates the new values of the registers, the memory (for store instructions), and the next program counter. Calls and returns are treated a bit differently: they do not directly transition from an instruction state to the next instruction state—they go through an intermediate call/return state.

In more detail, if the next instruction is a call instruction, rule (CALL1) looks up the function in the global environment, evaluates its arguments, creates a new stack frame corresponding to the current instruction state, and transitions to a call state. From a call state, there are two possible execution steps. If the function to be called is internal, *i.e.*, we have its function definition  $fd \in FDef$ , rule (CALL2-INTERNAL) applies. It allocates the necessary stack space for the called function, initializes the parameter registers with the values passed as arguments, sets the program counter to point to the first node of the called function, and moves to the appropriate instruction state of the called function. If the function to be called is external, *i.e.*, we have a function signature  $fs \in FSig$ , rule (CALL2-EXTERNAL) goes directly to the return state, and generates an event  $\sigma$  indicating that it called an external function.

Conversely, rule (RETURN1) returns from a function by evaluating the result to be returned, deallocating the stack space used by the function, and transitioning to the return state. Then rule (RETURN2) pops the top-most stack frame and transitions to a normal instruction state thereby restoring the registers, program counter, and stack pointers of the calling function.

#### 2.4 Constant Propagation

Now we explain how CompCert's constant propagation works, and how it verifies the optimization using the simulation technique.

**Algorithm** Given a program prg, constant propagation walks through each function definition fd of the program and transforms it using the function transfun(prg, fd). This in turn runs a "value analysis" to determine which variables (whether global variables or local registers) hold a known constant value at each program point and then, based on that information, simplifies the program.

The analysis consists of two parts: (a) the global part, which detects which global variables cannot be updated (*i.e.*, those declared with the const qualifier), and (b) the local part, which analyzes the code of a function and calculates an abstract value for each register and stack variable. The abstract value of a variable can be either  $\bot$  if the variable holds undef, or a constant number, or *NS* if the variable contains anything except for a pointer pointing into the current stack frame, or  $\top$  if no more precise information is

known. These abstract values form a lattice by taking the order  $\bot \sqsubseteq num \sqsubseteq NS \sqsubseteq \top$ .

The value analysis performs a usual traversal of the code. When calling a function, if it can be determined that no memory address can point to the current stack frame and none of the function's arguments point to the current stack frame (*i.e.*, their abstract value is at most *NS*), then the abstract value of the function's result is also *NS*, and the abstraction of the stack memory is preserved. If, however, a pointer to the current stack frame has escaped, then any information about the stack memory is forgotten.

The transformation part itself is straightforward: at each node n of the function's CFG, if the analysis has determined that a variable has a constant value at node n, then the use of that variable is replaced by the constant it holds, and the instruction is suitably simplified.

For example, the algorithms works for the constant propagation example presented in Section 3 as follows (albeit presented for a different language). First, the analysis result for x is the constant number 42 after line 10, and it continues to be 42 after line 20 because the address of x is not leaked to the external function. Then based on this analysis result, CompCert replaces x with 42 at line 30.

As a more interesting example, Figure I.5 shows the effect of constant propagation applied to a simple program. The program contains one internal function, f, which calls an external function, g, and three zero-initialized variables: a local variable (a register), x, an address-taken variable on the stack, sp[0], and a global variable, gv[0]. After the external function call, constant propagation can safely assume that x = 0 and thereby simplify the conditional at node 5, but cannot do the same for sp[0] at node 4 because its address was passed to the external function and its value might therefore have changed. Further, at node 6, constant propagation notes that the global variable gv[0] has been declared with the const qualifier, and can therefore assume that gv[0] = 0.

**Verification** The correctness proof of the constant propagation pass in CompCert establishes the existence of a simulation relation, R, that relates the loading of the source and target programs. That is, for every well-formed source RTL program prg, it proves there exists a simulation R(prg) such that  $(load(prg), load(\mathcal{T}_{cp}(prg))) \in R(prg)$ .

The simulation relation, R, used for the constant propagation pass is given in Figure I.6. It is defined in terms of matching relations on states, stack frames, and stacks and function definitions ( $\sim_{\text{state}}$ ,  $\sim_{\text{frame}}$ ,  $\sim_{\text{stack}}$ , and  $\sim_{\text{fdef}}$  respectively). These relations take as a parameter the source program, prg, which is used to relate the function definitions of the source and target programs.<sup>5</sup>

<sup>&</sup>lt;sup>5</sup>The version shown here is a slight simplification of the actual simulation used in the constant propa-

```

extern q(a,b);

extern q(a,b);

const qv[1] := \{ 0 \};

const qv[1] := \{ 0 \};

f() {

f() {

x, y;

x, y;

sp[4];

sp[4];

1: sp[0] := 0 imp 2;

1: sp[0] := 0 imp 2;

2: x := 0 \text{ jmp } 3;

2: x := 0 \text{ jmp } 3;

3: y := g(sp,x) jmp 4;

3: y := g(sp,x) jmp 4;

4: sp[0] > 0 ? jmp 5 : jmp 6;

4: sp[0] > 0 ? jmp 5 : jmp 6;

// CHANGED

5: x > 0 ? jmp 6 : jmp 7;

\mapsto

5: jmp 7;

6: return qv[0];

6: return 0;

// CHANGED

7: return y;

7: return y;

}

}

```

Figure I.5 Example of constant propagation

We say that two function definitions are related in the program prg, written  $fd \sim_{fdef} fd'$ , if the target function, fd', is the result of applying constant propagation to the source function, fd. Two stack frames are related by  $prg \vdash sf \sim_{frame} sf'$  if the function code in sf' is the transformation of the function code of sf, the stack pointer and program counters agree, and the registers of sf' hold equal or more defined values than those of sf. Two stacks are related,  $prg \vdash s \sim_{stack} s'$ , if they have the same length and their stack frames are related element-wise.

Two states are related,  $prg \vdash s \sim_{\text{state}} s'$  if (1) they are of the same kind, (2) the memory of s' is an extension of that of s, (3) their stacks are related by  $\sim_{\text{stack}}$ , (4) the respective function definitions are related by  $\sim_{\text{fdef}}$  (when applicable), (5) the stack pointer and program counter agree (when applicable), and (6) the registers/arguments/return value of s is equal or less defined than that of s'.

Finally, the two states are in the simulation relation R if they are related by  $\sim_{\text{state}}$  and the source state satisfies the value analysis invariant, sound-state(prg, s). This invariant basically says that the (concrete) value of each variable in the state s is included in the variable's abstract value computed by the analysis at the current program point. The invariant depends on the program for two reasons: (1) so that it can calculate the global environment, ge = get - genv(prg), and (2) so that it can 'run' the analysis on the program so as to be able to compare its results with the current state.

The basic soundness properties of the value analysis are (1) that the sound-state

gation pass. It abstracts away some tedious details of the actual  $\sim_{\rm frame}$  definition that are orthogonal to our story. This is merely to streamline the presentation.

$$prg \vdash fd \sim_{fdef} fd' \stackrel{\text{def}}{=} fd' = \operatorname{transfun}(prg, fd)$$

$$\frac{prg \vdash fd \sim_{fdef} fd' \qquad rs \leq_{\operatorname{def}} rs'}{prg \vdash (r, fd, sp, pc, rs) \sim_{\operatorname{frame}} (r, fd', sp, pc, rs')}$$

$$\frac{prg \vdash sf \sim_{\operatorname{frame}} sf' \qquad s \sim_{\operatorname{stack}} s'}{prg \vdash sf ::s \sim_{\operatorname{stack}} sf ::s'}$$

$$\frac{m \sqsubseteq_{\operatorname{ext}} m' \qquad s \sim_{\operatorname{stack}} s' \qquad prg \vdash fd \sim_{\operatorname{fdef}} fd' \qquad rs \leq_{\operatorname{def}} rs'}{prg \vdash \operatorname{ist} m \ s \ fd \ sp \ pc \ rs \sim_{\operatorname{state}} \operatorname{ist} m' \ s' \ fd' \ sp \ pc \ rs'}$$

$$\frac{m \sqsubseteq_{\operatorname{ext}} m' \qquad s \sim_{\operatorname{stack}} s' \qquad prg \vdash fd \sim_{\operatorname{fdef}} fd' \qquad args \leq_{\operatorname{def}} args'}{prg \vdash \operatorname{cst} m \ s \ fd \ args \sim_{\operatorname{state}} \operatorname{cst} m' \ s' \ fd' \ args'}$$

$$\frac{m \sqsubseteq_{\operatorname{ext}} m' \qquad s \sim_{\operatorname{stack}} s' \qquad v \leq_{\operatorname{def}} v'}{prg \vdash \operatorname{rst} m \ s \ v \sim_{\operatorname{state}} \operatorname{rst} m' \ s' \ v'}$$

$$(s,s') \in R(prg) \stackrel{\operatorname{def}}{=} prg \vdash s \sim_{\operatorname{state}} s' \wedge \operatorname{sound-state}(prg,s)$$

Figure I.6 CompCert's simulation relation for the constant propagation

invariant holds for the initial state of a program, and (2) that it is preserved by execution steps. Formally:

$$\frac{s = load(prg)}{\text{sound-state}(prg, s)} = \frac{s = load(prg)}{\text{sound-state}(prg, s)} = \frac{s = load(prg)}{s = get - genv(prg)} = \frac{s \to ge}{s \to ge} = \frac{s'}{s}$$

The CompCert proof then establishes the following two properties of *R*, which collectively imply compiler correctness, *i.e.*, the target's behaviors refine the source's:

- (1)  $(load(prg), load(\mathcal{T}_{CD}(prg))) \in R$ .

- (2) R is indeed a simulation relation. Specifically, it is a "backward" simulation, meaning that for any related states  $(s, t) \in R$ , if the target state t takes a step to t' with an event  $\sigma$ , the source s also takes a step to *some* state s' with the same event  $\sigma$ , such that  $(s', t') \in R$ .

As for (1), the initial states after loading satisfy  $\sim_{\text{state}}$  by construction, and the initial source state satisfies sound-state thanks to the soundness of the value analysis above. As for (2), R is indeed a backward simulation for the following reasons. From  $(s, t) \in R$ , we know that we are executing the instructions at the same pc. Thus by the definition of constant propagation, the target instruction is either identical to the source instruction or obtained by replacing a variable with a constant or converting a conditional jump to an unconditional jump, depending on the value analysis result. Here, thanks to the soundness of the current state w.r.t. the analysis result and the relation between the two states specified by  $\sim_{\text{state}}$ , we can easily deduce that executing the source and target instructions results in related states. Also, the soundness of the new source state s' follows from the soundness preservation property of the value analysis stated above.

Note: The verification approach described above, relying on backward simulations, is something of an oversimplification of what CompCert actually does. In fact, to make the proofs more convenient, CompCert uses "forward" simulations for the backend passes. We briefly discuss why CompCert uses forward simulation, even though it implies that the source's behaviors refine the target's, which seems the wrong way around. First, a forward simulation is easier to establish than a backward one because a single instruction in the source may be compiled down to several instructions in the target. Second, CompCert composes forward simulations of backend passes using the transitivity of forward simulations, which is not hard to show. Then it converts the composed forward simulation between an IR and assembly to a backward simulation between them

using some technical properties of the IR and assembly (namely, that the IR is "receptive" and assembly is "determinate"). Finally, from this backward simulation, one can establish that the target's behaviors refine the source's.

So far we discussed the technical background that is needed to understand the main contributions of this dissertation, which we will present from now on. We will start with a formal semantics of casts between integers and pointers.

# **Chapter II**

# **Relaxed-Memory Concurrency**

# 3 Introduction

What is the right semantics for concurrent shared-memory programs written in higher-level languages? For programmers, the simplest answer would be a *sequentially consistent (SC)* semantics, in which all threads in a program share a single view of memory and writes to memory take immediate global effect.

However, a naive SC semantics is costly to implement. First of all, commodity architectures (such as x86, Power, and ARM) are not SC: they execute memory operations speculatively or out of order, and they employ hierarchies of buffers to reduce memory latency, with the effect that there is no globally consistent view of memory shared by all threads. To simulate SC semantics on these architectures, one must therefore insert expensive fence instructions to subvert the efforts of the hardware. Secondly, a number of common compiler optimizations—such as constant propagation—are rendered unsound by a naive SC semantics because they effectively reorder memory operations. Moreover, SC semantics is stronger (*i.e.*, more restrictive) than necessary for many concurrent algorithms.

Hence, languages like C/C++ and Java have opted instead to provide *relaxed* (aka *weak*) memory models [59, 36], which enable programmers to demand SC semantics when they need it, but which also support a range of cheaper memory operations that trade off strongly consistent and/or well-defined behavior for efficiency.

#### 3.1 Criteria for a Programming Language Memory Model

Unfortunately, despite many years of research, it has proven very difficult to develop a memory model for concurrent programming languages that adequately balances the conflicting desiderata of programmers, compilers, and hardware. In particular, we would like to find a memory model that satisfies the following properties:

- The model should support *high-level reasoning* principles that programmers and compiler analyses depend on. At a bare minimum, it should validate simple invariant-based verification, and should provide some "DRF" guarantees [10], ensuring that programmers who employ sufficient synchronization need not understand the full complexities of relaxed-memory semantics.

- The model should be *implementable*, *i.e.*, it should validate common compiler optimizations, as well as standard compilation schemes to the major modern architectures. To be implementable, it must justify many kinds of instruction reordering and merging.

- The model should ideally avoid relying on undefined behavior to define the semantics of racy programs. This is a prerequisite for applicability to type-safe languages like Java, in which well-typed programs may contain data races but are nevertheless expected to have safe, well-defined semantics.

Both C/C++ and Java fail to achieve some of these criteria.