# **Promising 2.0: Global Optimizations** in Relaxed Memory Concurrency

Sung-Hwan Lee Seoul National University Korea sunghwan.lee@sf.snu.ac.kr Minki Cho Seoul National University Korea minki.cho@sf.snu.ac.kr Anton Podkopaev National Research University Higher School of Economics & MPI-SWS Russia & Germany podkopaev@mpi-sws.org Soham Chakraborty

IIT Delhi

India

soham@cse.iitd.ac.in

Chung-Kil Hur Seoul National University Korea gil.hur@sf.snu.ac.kr Ori Lahav

Tel Aviv University

Israel

orilahav@tau.ac.il

Viktor Vafeiadis MPI-SWS Germany viktor@mpi-sws.org

## **Abstract**

For more than fifteen years, researchers have tried to support global optimizations in a usable semantics for a concurrent programming language, yet this task has been proven to be very difficult because of (1) the infamous "out of thin air" problem, and (2) the subtle interaction between global and thread-local optimizations.

In this paper, we present a solution to this problem by redesigning a key component of the *promising semantics* (PS) of Kang et al. Our updated PS 2.0 model supports all the results known about the original PS model (*i.e.*, thread-local optimizations, hardware mappings, DRF theorems), but additionally enables transformations based on global value-range analysis as well as register promotion (*i.e.*, making accesses to a shared location local if the location is accessed by only one thread). PS 2.0 also resolves a problem with the compilation of relaxed RMWs to ARMv8, which required an unintended extra fence.

CCS Concepts: • Theory of computation  $\rightarrow$  Concurrency; Operational semantics; • Software and its engineering  $\rightarrow$  Semantics.

*Keywords:* Relaxed Memory Concurrency; Operational Semantics; Compiler Optimizations

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than the author(s) must be honored. Abstracting with credit is permitted. To copy otherwise, or republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from permissions@acm.org. PLDI '20, June 15–20, 2020, London, UK

@ 2020 Copyright held by the owner/author(s). Publication rights licensed to ACM.

ACM ISBN 978-1-4503-7613-6/20/06.

https://doi.org/10.1145/3385412.3386010

#### **ACM Reference Format:**

Sung-Hwan Lee, Minki Cho, Anton Podkopaev, Soham Chakraborty, Chung-Kil Hur, Ori Lahav, and Viktor Vafeiadis. 2020. Promising 2.0: Global Optimizations in Relaxed Memory Concurrency. In Proceedings of the 41st ACM SIGPLAN International Conference on Programming Language Design and Implementation (PLDI '20), June 15–20, 2020, London, UK. ACM, New York, NY, USA, 15 pages. https://doi.org/10.1145/3385412.3386010

## 1 Introduction

A major challenge in programming language semantics has been to define a weak memory model for a concurrent programming language supporting efficient compilation to the mainstream hardware platforms (*i.e.*, x86, POWER, ARMv7, ARMv8, RISC-V) including all applicable compiler optimizations and yet avoiding semantics quirks, such as "out of thin air" reads [16], that prevent formal reasoning about programs and break DRF guarantees (the latter provide simpler semantics to data-race-free programs). In particular, such a semantics must allow the following annotated outcome (assuming all variables are initialized to zero and all accesses are relaxed).

$$a := x //1 \mid b := y //1 y := 1 \mid x := b$$

(LB)

This outcome is observable after a compiler transformation that reorders the (independent) accesses of thread 1, while on ARM [20] it is even observable without the transformation.

While there are multiple partial solutions to this challenge [7, 8, 12, 16, 18], none of them properly supports global compiler optimizations, namely program transformations whose validity depends on some global analysis. Examples of such transformations are (a) removal of null pointer checks based on global null-pointer analysis; (b) removal of array bounds checks based on global size analysis; and (c) *register promotion*, *i.e.*, converting accesses to a shared variable that happens to be used by only one thread to local accesses. The latter is very important in languages like Java that have only

atomic accesses, but is also useful for C/C++. For instance, in single-threaded programs, it allows the removal of locks, as well as the promotion to register accesses of inlined function calls of concurrent data-structures.

The desire to support global optimizations in concurrent programming languages goes at least as back as 15 years ago with the Java memory model (JMM) [16]. In fact, the very first JMM "causality test case" is centered around valuerange analysis. Assuming all variables are initialized to 0, JMM allows the annotated outcome of the following example:

$$a := x \text{ } /\!\!/ 1$$

if  $a \ge 0$  then

$$y := 1$$

$$b := y \text{ } /\!\!/ 1$$

$$x := b$$

(JMM1)

"Decision: Allowed, since interthread compiler analysis could determine that x and y are always nonnegative, allowing simplification of  $a \ge 0$  to true, and allowing write y := 1 to be moved early." [10]

Supporting global optimizations, however, is rather challenging because of their interaction with local transformations. Global optimizations generally depend on invariants deduced by some global analysis but these invariants need not hold in the source program; they might hold after some local transformations have been applied. In the following example, (only) after the local elimination of the overwritten x := 42 assignment, the condition a < 10 becomes a global invariant, and so can be simplified to true as in JMM1.

$$a := x //1$$

**if**  $a < 10$  **then**  $y := 1$   $x := 42$

$b := y //1$  (LB-G)

In more complex cases, a global optimization may enable a local transformation, which may further enable another global optimization, which may enable another local optimization, and so on. As a result, supporting both global and local transformations is very difficult, and none of the solutions so far has managed to fully support global analysis along with all the expected thread-local transformations.

In this paper, we present the first memory model that solves this challenge: (i) it allows the aforementioned global optimizations (value-range analysis and register promotion); (ii) it validates the thread-local compiler optimizations that are validated by the C/C++11 model [13] (e.g., roach-motel reorderings [21]); (iii) it can be efficiently mapped to the mainstream hardware platforms (x86, POWER, ARMv7, ARMv8, RISC-V); and (iv) it supports reasoning principles in the form of DRF guarantees, allowing programmers to resort to simpler well-behaved models when data races are appropriately restricted. In developing our model we mainly use (i)–(iii) to conclude that some behavior should be allowed; while (iv) tells us which behaviors must be forbidden.

As a starting point, we take the *promising semantics* (PS) of Kang et al. [12], a concurrency semantics that satisfies *almost* all our desiderata. It supports almost all C/C++11

features, all expected thread-local compiler optimizations, and several DRF theorems. In addition, Podkopaev et al. [19] established the correctness of a mapping from PS to hardware. The main drawback of PS is that it does not support global optimizations.

PS is an operational semantics which represents shared memory as a set of messages (*i.e.*, writes). To support out-of-order execution, PS employs a non-standard step, allowing a thread to *promise* to perform a write in the future, which enables other threads to read from it before the write is actually executed.

The technical challenge resides in identifying the exact conditions on such promise steps so that basic guarantees (like DRF and no "thin-air values") are maintained.

In PS, these conditions are completely thread-local: the thread performing the promise must be able to run in isolation from *all extensions* of the current state and fulfill all its outstanding promises. While thread-locality is useful, quantifying over all extensions of the current state prevents optimizations based on global analysis because some extensions may well not satisfy the invariant produced by the analysis.

Checking for promise fulfillment only from the current state without extension enables global analysis, but breaks the DRF guarantee (see §4). Our solution is therefore to check promise fulfillment for a carefully crafted extension of the current state, which we call *capped memory*. Because capped memory does not contain any new values, it is consistent with optimizations based on global value analysis. However, it still does not allow optimizations like register promotion.

To support register promotion, we introduce *reservations*, which allow a thread to secure an exclusive right to perform an atomic read-modify-write instruction reading from a certain message without fixing the value that it will write (because, for example, that might not have yet been resolved). In addition, reservations resolve a problem with the compilation of PS to ARMv8, whose intended mapping of RMWs was unsound and required an extra fence [19].<sup>2</sup>

With these two new concepts, we are able to retain the thread-local nature of PS and yet fully support global optimizations and the intended mapping of RMWs along with all the results available for PS. Our redesigned PS 2.0 model is the first weak memory model that achieves these results. To establish confidence in our model, we have formalized our key results in the **Coq proof assistant**.

*Outline.* In the following, we first review the PS definition (§2), and why it does not support global optimizations

<sup>&</sup>lt;sup>1</sup>Albeit, the mapping of RMWs to ARMv8 contains one more barrier ("ld fence") than intended because the intended mapping is unsound.

<sup>&</sup>lt;sup>2</sup>Our current mechanized proof requires a fake control dependency from relaxed fetch-and-add instructions, which is currently not added by standard compilers. We believe that the compilation from our model without this dependency is sound as well, and leave the formal proof to a future work (see also §6.5).

(§3). We then present our PS 2.0 model both informally in an incremental fashion (§4) and formally all together (§5). In §6, we establish the correctness of mappings from PS 2.0 to hardware, and show that PS 2.0 supports all the local transformations and reasoning principles known to be allowed by PS, as well as register promotion, and the introduction of 'assert' statements for invariants derived by global analysis. The mechanization of our main results in Coq, the full model definitions, and written proofs of additional claims are available in [1].

## 2 Introduction to the Promising Semantics

In this section, we introduce the promising semantics (PS) of Kang et al. [12]. For simplicity, we present only a fragment of PS containing only three kinds of memory accesses: relaxed (the default mode), release writes (rel), and acquire reads (acq). Read-modify-write (RMW) instructions, such as compare-and-swap (CAS) and fetch-and-add (FADD), carry two access modes—one for the exclusive read and one for the write. We put aside other access modes, fences, and release sequences, as they are orthogonal to the contribution of this paper. We refer the reader to [12] for the full PS model.

**Domains.** We assume non-empty sets Loc of locations and Val of values. We also assume a set Time of *timestamps*, which is totally and densely ordered by < with 0 as its minimum. (In our examples, we take non-negative rational numbers as timestamps with their usual ordering.) A *view*,  $V \in \text{View} \triangleq \text{Loc} \rightarrow \text{Time}$ , records the largest known timestamp for each memory location. A timestamp *interval* is a pair of timestamps (f,t] with f < t or f = t = 0. It represents the range of timestamps from (but not including) f up to and including t.

*Memory.* In PS, the memory is a set of *messages* representing all previously executed writes. A message m is of the form  $\langle x:v@(f,t],R\rangle$ , where  $x\in \text{Loc}$  is the location,  $v\in \text{Val}$  is the stored value, (f,t] is a timestamp interval, and  $R\in \text{View}$  is the message view. The latter is used to model release-acquire synchronization and will be explained shortly. Initially, the memory consists of an initialization message for every location carrying the value 0, the interval (0,0], and the bottom view  $\bot\triangleq \lambda x$ . 0. We require that any two messages with the same location in memory have disjoint timestamp intervals. The timestamp (also called the "to"-timestamp) of a massage  $\langle x:v@(f,t],R\rangle$  is the upper bound t of the message's timestamp interval. The lower bound t, called the "from"-timestamp, is needed to handle atomic updates (a.k.a. RMW operations) as explained below.

*Machine State.* PS is an operational model where threads execute in an interleaved fashion. The *machine state* is a pair  $\Sigma = \langle \mathcal{TS}, M \rangle$ , where  $\mathcal{TS}$  assigns a *thread state TS* to every thread and M is a (global) *memory*. A thread state is a triple  $TS = \langle \sigma, V, P \rangle$  where  $\sigma$  is the local store recording the values

of its local variables,  $V \in View$  is the *thread view*, and P is a set of messages representing the thread's outstanding promises.

**Relaxed Reads and Writes.** Thread views are instrumental in providing correct semantics to memory accesses. The thread view, V, records the "knowledge" of each thread, *i.e.*, the timestamp of the most recent message that it has observed for each location. It is used to forbid a thread to read from a (stale) message m if the thread is aware of a "newer" message, *i.e.*, when V(x) is greater than the message's timestamp. Similarly, when a thread adds messages of location x to the memory, it has to pick a timestamp t for the added message that is greater than its view of x (V(x) < t):

**READ.** A thread can read from memory M by simply observing a message  $\langle x : v@(f,t], \_ \rangle \in M$  provided that  $V(x) \le t$ , and updating its view for x to t.

**WRITE**. A thread adds a new message  $m = \langle x : v@(f, t], \bot \rangle$  to the memory where the timestamp t is greater than the thread's view of x (V(x) < t) and there is no other message with the same location and overlapping timestamp interval in the memory. Relaxed writes set the message view to  $\bot$ , which maps each location to timestamp 0.

The following example illustrates how timestamps of messages and views interact. Note that we assume that both threads start with the initial thread view that maps x and y to 0, and that every location is initialized to 0: the initial memory only contains messages  $\langle x:0@(0,0],\bot\rangle$  and  $\langle y:0@(0,0],\bot\rangle$ .<sup>3</sup>

$$x := 1$$

$a := y //0 || y := 1$

$b := x //0$  (SB)

Here, both threads are allowed to read from the initialization messages, 0. When thread 1 performs the write to x, it will add a message  $\langle x:0@(f,t],\bot\rangle$  by choosing some  $t>f\geq 0$ . During this write, thread 1 should increase its view of x to t, while maintaining V(y) to be 0 as it was. Hence, thread 1 is still allowed to read 0 from y in the subsequent execution. As thread 2 can be executed in the same way, both threads are allowed to read 0.

**Relaxed Atomic Updates.** Atomic updates (a.k.a. RMW operations) are essentially a pair of accesses to the same location—a read followed by a write—with an additional atomicity guarantee: the read reads from a message that immediately precedes the one added by the write. PS employs timestamp intervals (rather than single timestamps) to enforce atomicity.

**UPDATE**. When a thread performs an RMW, it first reads a message  $\langle x : v@(f,t], \bot \rangle$ , and then writes the updated message with "from"-timestamp equal to t, *i.e.*, a message of the form  $\langle x : v'@(t,t'], \bot \rangle$ . This results in consecutive messages

$<sup>^3</sup>$ In all our code examples, we assume that all memory accesses are relaxed (rlx memory order) unless annotated otherwise.

(f, t], (t, t'], forbidding other writes to be later placed between the two messages (recall that messages with the same location must have disjoint timestamp intervals).

This constraint, in particular, means that two competing RMWs cannot read from the same message, as the following "parallel increment" example demonstrates.<sup>4</sup>

$$a := \text{FADD}(x, 1) / 0 \mid b := \text{FADD}(x, 1) / 0$$

(Upd)

Without loss of generality, suppose that thread 1 executed first. As it performs an RMW operation, it must "attach" the message it adds to an existing message. Since the only existing message in this stage is the initial one  $\langle x:0@(0,0],\bot\rangle$ , thread 1 will first add a message  $m=\langle x:1@(0,t],\bot\rangle$  with some t>0 to the memory. Then, the RMW of thread 2 cannot also read from the initial message because its interval would overlap with the (0,t] interval of m. Therefore, the annotated behavior is forbidden. More abstractly speaking, the timestamps intervals of PS express a dense total order on messages to the same location together with immediate adjacency constraints on this order, which are required for handling RMW operations.

Release and Acquire Accesses. To provide the appropriate semantics to release and acquire accesses, PS uses the message views. Indeed, a release write should transfer the current knowledge of the thread to other threads that read the message by an acquire read. Thus, (i) a release write operation puts the current thread view in the message view of the added message; and (ii) an acquire read operation incorporates the view of the message being read in the thread view (by taking the pointwise maximum).

**READ** is defined the same as before, except that when the thread performs an *acquire* read, it increases its view to contain not only the ("to") timestamp of the message read but also the view of that message.

**WRITE** is defined as before, except that *release* writes record the thread view in the message being added, whereas relaxed writes record the  $\perp$  view.

As a result, the acquiring thread is confined in its future reads at least as the releasing thread was confined when it "released" the message being "acquired". As a simple example, consider the following:

$$x := 1$$

$$y^{\text{rel}} := 1$$

$$\begin{vmatrix} a := y^{\text{acq}} //1 \\ \text{if } a = 1 \text{ then} \\ b := x //0 \end{vmatrix}$$

(MP)

Here, if thread 2 reads 1 from y, which is written by thread 1, both threads are synchronized through release and acquire. Thus, thread 2 obtains the knowledge of thread 1, namely its view for x is increased to include the timestamp of x := 1 of thread 1. Therefore, after reading 1 from y, thread 2 is not allowed to read the initial value 0 from x.

Release/acquire RMW operations also transfer thread views via message views as release writes and acquire reads do.

**Promises.** The main novelty of PS lies in its way to enable the reordering of a read followed by a write (of different locations), needed to explain the outcome of the LB program in §1. Thus, besides step-by-step program execution, PS allows threads to non-deterministically *promise* their future writes. This is done by simply adding a message (whose interval does not overlap with that of any existing message to the same location) to the memory. Later, the execution of write instructions may also *fulfill* an existing promise (rather than add a message to the memory). Thread promises are kept in the thread state, and removed when the promise is fulfilled. Naturally, at the end of the execution all promises must be fulfilled.

**PROMISE**. At any point, a thread can add a message to both its set of promises and the memory.

**FULFILL**. A thread can fulfill its promise by executing a (non-release) write instruction, by removing a message from the thread's set of promises. PS does not allow release writes to be promised, *i.e.*, a promise cannot be fulfilled through a release write instruction.

In the LB program above, thread 1 may promise y := 1 at first. This allows thread 2 to read 1 from y and write it back to x. Then, thread 1 can read 1 from x, which was written by thread 2, and fulfill its promise.

**Certification.** To ensure that promises do not make the semantics overly weak, each sequence of steps by a thread (before "yielding control to the scheduler") has to be *certified*: the thread that took the steps should be able to fulfill all its promises when executed in isolation. Indeed, revisiting the LB program above, note that at the point of promising y := 1 (in the very beginning of the run), thread 1 can run and perform y := 1 without any "help" of other threads.

Certification (*i.e.*, the thread-local run fulfilling all outstanding promises of the thread) is necessary to avoid "thinair reads" as demonstrated by the following variant of LB:

$$a := x //1$$

$b := y //1$   $y := a$  (OOTA)

As every thread simply copies the value it reads, both threads are not supposed to read any other value than 0 from the memory. However, the annotated behavior, often called out-of-thin-air, is allowed in C11 [3]. In PS, if a thread could promise without certification, this behavior would be allowed by the same execution as the one for LB. However, with the certification requirement, thread 1 cannot promise y := 1, as, when running in isolation, thread 1 will only write y := 0.

PS requires a certification to exist for *every future memory* (*i.e.*, any memory that extends the current memory). In §3, we explain the reason for this condition and its consequences.

<sup>&</sup>lt;sup>4</sup>Here and henceforth, we assume that RMW instructions such as **FADD** and **CAS** return the value that was read during the read-modify-write operation (before the update).

**Machine Step.** A thread configuration  $\langle TS, M \rangle$  can take one of **READ**, **WRITE**, **UPDATE**, **PROMISE**, and **FULFILL** steps, denoted by  $\langle TS, M \rangle \rightarrow \langle TS', M' \rangle$ . In addition, a thread configuration is called *consistent* if for every future memory  $M_{\text{future}}$  of M, there exist TS' and M' such that (where TS.prm denotes the set of outstanding promises in thread state TS):

$$\langle TS, M_{\text{future}} \rangle \rightarrow^* \langle TS', M' \rangle \land TS'.\text{prm} = \emptyset$$

In turn, the machine step is defined as follows:

$$\frac{\langle \mathcal{TS}(i), M \rangle \to^{+} \langle \mathit{TS'}, M' \rangle}{\langle \mathit{TS'}, M' \rangle \text{ is consistent}}$$

$$\frac{\langle \mathcal{TS}, M \rangle \to \langle \mathcal{TS}[i \mapsto \mathit{TS'}], M' \rangle}{\langle \mathcal{TS}, M \rangle \to \langle \mathcal{TS}[i \mapsto \mathit{TS'}], M' \rangle}$$

We note that the machine step is completely *thread-local*: it is only determined by the local state of the executing thread and the global memory, independently of the other threads' states. Thread-locality is a key design principle of PS. It is what makes PS conceptually well-behaved, and, technically speaking, it allows one to prove the validity of various local program transformations, which are performed by compilers and/or hardware, using standard thread-local simulation arguments.

To show a concrete example, we list the execution steps of PS leading to the annotated behavior of the LB program (items prefixed with "C" represent certification steps):

- (1) Thread 1 promises  $\langle y : 1@(1,2], \perp \rangle$ .

- (C1) Starting from an arbitrary extension of the current memory, thread 1 reads  $\langle x:0@(0,0],\bot\rangle$ , the initial message of x.

- (C2) Thread 1 fulfills its promise  $\langle y: 1@(1,2], \perp \rangle$ .

- (2) Thread 2 reads  $\langle y : 1@(1,2], \perp \rangle$ .

- (3) Thread 2 writes  $\langle x : 1@(1,2], \perp \rangle$ .

- (4) Thread 1 reads  $\langle x : 1@(1,2], \perp \rangle$ .

- (C1) Starting from an arbitrary extension of the current memory, Thread 1 fulfills its promise  $\langle y : 1@(1, 2], \bot \rangle$ .

- (5) Thread 1 fulfills its promise  $\langle y: 1@(1,2], \perp \rangle$ .

**DRF-RA Guarantee.** We end this introductory section by informally describing DRF-RA, one of the main programming guarantees provided by PS. Generally speaking, DRF guarantees ensure that race-free programs have strong (*i.e.*, more restrictive) semantics. To be more applicable and allow their use without even knowing the weaker semantics, race freedom is checked assuming the strong semantics.

In particular, DRF-RA is focused on release/acquire semantics (RA), and states that: if under RA semantics some program *P* has no data race involving relaxed accesses (*i.e.*, all races are on rel/acq accesses), then all behaviors that PS allows for *P* are also allowed for *P* by the RA semantics. Here, (i) by RA semantics we mean the model obtained from PS by treating *all* reads as acq reads, all writes as rel writes, and all RMWs as acqrel; and (ii) as PS is an operational model, data-races are naturally defined as states in which

two different threads can access the same location and at least one of these accesses is writing.

For example, by analyzing the MP example under RA semantics, one can easily observe that the only race is on the rel/acq accesses to y. (Importantly, such analysis safely ignores promises, since these are not allowed under RA.) Then, DRF-RA implies that MP has only RA behaviors. In contrast, in the LB example, non-RA behaviors are possible, and, indeed, under RA semantics, there are races on relaxed accesses (to both x and y).

In the sequel, DRF-RA provides us with the main guideline for making sure that our semantics is not overly weak (that is, we exclude any semantics that breaks DRF-RA). DRF-RA also serves as a main step towards "DRF-Lock", which states that properly locked programs have only sequentially consistent semantics.<sup>5</sup>

## 3 Problem Overview

As we will shortly demonstrate, the main challenge in PS is to come up with an appropriate thread-local condition for certifying the promises made by a thread. Maintaining thread-locality is instrumental in proving correctness of many compiler transformations, but is difficult to achieve given that promises of different threads may interact.

As we briefly mentioned above, PS requires a certification to exist for any memory that extends the current memory. We start by explaining why certifying promises only from the current memory (without quantifying over all future memories) is not good enough. Kang et al. [12] observed that such model may deadlock: the promising thread may fail to fulfill its promise since the memory was changed since the promise was made. In this work, we observe that a model that requires certifying promises only from the current memory has much more severe consequences. It actually *breaks the DRF-RA guarantee* as illustrated below:

Under RA semantics only one thread can enter the if-branch, and the only race is between the two **FADD**s. Hence, to maintain DRF-RA, we need to disallow the annotated behavior where both threads read 0 from x. To prevent this behavior, we need to disallow thread 1 to promise y := 1 in the beginning of the run. Indeed, by reading such a promise, thread 2 can write x := 0, and then, thread 1 can perform its update to x and fulfill its outstanding promise. However, if we completely ignore the possible interference by other

<sup>&</sup>lt;sup>5</sup>The more standard DRF-SC, guaranteeing sequentially consistent semantics when all races (assuming SC semantics) are on SC accesses, is not applicable here since PS lacks SC accesses. The extension of PS with SC accesses is left to future work.

threads, thread 1 may promise y := 1, as it can be certified in a local run of thread 1 that starts from the initial memory and reads the initial message of x.

Abstractly, what went wrong is that two threads compete on the same resource (*i.e.*, to perform an RMW reading from the initialization message); one of them makes a promise assuming it will get the resource first but the other thread wins the competition in the actual run. This not only causes deadlock (which is semantically inconsequential), but also breaks DRF-RA.

To address this, PS followed a simple approach: it required that threads certify their promises starting from *any* extension of the current memory. One such particular extension is the memory that will arise when the required resource is acquired by some other thread. Hence, this condition does not allow threads to promise writes assuming they will win a competition on some resource.

Revisiting CDRF, PS's certification condition blocks the promise of y:=1. For example, when certifying against  $M_{\text{future}}$  that, in addition to the initialization messages, consists of a message  $m=\langle x:42@(0,\_],\_\rangle$ , thread 1 is forced to read from m when performing its **FADD**, and cannot fulfill its promise. Since  $M_{\text{future}}$  is a possible future memory of the initial memory, thread 1 cannot promise y:=1.

PS's future memory quantification maintains the threadlocality principle and suffices for establishing DRF-RA. However, next, we demonstrate that this very conservative overapproximation of possible interference is too strong to support global optimizations, and it is also the source of unsoundness of the intended compilation scheme to ARMv8.

**Value-Range Analysis.** PS does not support global optimizations based on value-range analysis. To see this, consider a variant of the LB-G program above that does not have the redundant store to x in thread 2 and has a **CAS** instruction in thread 1.

$$a := \mathbf{CAS}(x, 0, 1) //1$$

**if**  $a < 10$  **then**

$y := 1$   $b := y //1$

$x := b$  (GA)

In PS, the annotated behavior is disallowed. Indeed, to obtain this behavior, thread 1 has to promise y := 1. This promise, however, cannot be certified for every future memory  $M_{\rm future}$ . For example, if, in addition to the initialization messages, the future memory  $M_{\rm future}$  consists of a single message of the form  $\langle x : 57@(0, \_], \_\rangle$ , then the **CAS** instruction can only read 57, and the write y := 1 is not executed. However, by observing the global invariant  $x < 10 \land y < 10$ , a global compiler analysis may transform this program to the following:

$$a := \mathbf{CAS}(x, 0, 1) \ //1 \ | \ b := y \ //1 \ y := 1$$

Now, the annotated behavior is allowed (the promise y := 1 is not blocked anymore), rendering the optimization unsound. This is particularly unsatisfying because PS ensures that

x < 10 is globally valid in this program (via its "invariant logic" [12, §5.5]), but does not allow an optimizing compiler to make use of this fact.

**Register Promotion.** A similar problem arises for a different kind of global optimization, namely *register promotion*:

$$a := x \ // 1$$

$c := \text{FADD}(z, a) \ // 0$   $b := y \ // 1$

$u := 1 + c$  (RP)

PS disallows the annotated behavior. Again, thread 1 cannot promise y := 1, since an arbitrary future memory may not allow it to read z = 0 when performing the RMW. (Note also the RMW writing z := 1 cannot be promised before y := 1 since it requires to read x := 1 first.) Nevertheless, a global compiler analysis may notice that z is a local variable in the source program, and perform register promotion, replacing  $c := \mathbf{FADD}(z, a)$  with c := 0 (since this  $\mathbf{FADD}$  always returns 0). Now, PS *allows* the annotated behavior (nothing blocks the promise y := 1), rendering register promotion unsound.

Unsound Compilation Scheme to ARMv8. A different problem in PS, found while formally establishing the correctness of compilation to ARMv8 [19], is that the intended mapping of RMWs to ARMv8 is broken. In fact, this problem stems from the exact same reason as the two problems above.

While PS disallows the annotated behavior of the RP program above, when following the intended mapping to ARMv8 [6], ARMv8 allows the annotated behavior for the target program. Roughly speaking, although the instructions cannot be reordered at the source level, they can be reordered at the micro-architecture level. **FADD** is effectively turned into two special instructions, a load exclusive followed by a store exclusive. Since there is no dependency between the load of x and the exclusive load of z, the two loads could be executed out of order. Similarly, the two stores could be executed out of order, and so the store to y could effectively be executed before the load of x, which in turn leads to the annotated behavior.

**What went wrong?** These three problems all arise because PS's certification requirement against every memory extension is overly conservative in approximating the interference by other threads. The challenge lies in relaxing this condition in a way that will ensure the soundness of global optimizations while maintaining *thread-locality*.

As CDRF shows, simply relaxing the certification requirement by requiring certification only against the current memory is not an option. Another naive remedy would be to restrict the certification to extensions of the current memory that can actually arise in the given program. This approach, however, is bound to fail:

<sup>&</sup>lt;sup>6</sup>Here the fact that no other thread accesses z is immaterial. ARMv8 allows this behavior also when, say, a third thread executes z := 5.

• First, due to the intricate interaction with local optimizations, a precise approximation of other threads effect on memory is too strong—we may have a preceding local optimization that reduces the behaviors of the other threads. For instance, consider the following program:

$$a := \mathbf{CAS}(x, 0, 1) \ // 1$$

if  $a < 10$  then

$y := 1$

$x := 42$

$b := y \ // 1$

$x := b$  (GA+E)

Here, x := 42 occurs in a possible future memory, but a compiler may soundly eliminate this write.

• Second, this approach is not thread-local, and, since other threads may promise as well, it immediately leads to troublesome cyclic reasoning: whether thread 1 may promise a write depends on behavior of thread 2 that may include promise steps that again depend on behavior of thread 1.

#### 4 Solution Overview

In this section, we present the key ideas behind our modified PS model, which we call PS 2.0. Section 4.1 describes the notion of *capped memory*, which enables value-range analysis, while §4.2 discusses *reservations*, an additional mechanism needed to support register promotion and recover the correctness of the mapping to ARMv8. Section 4.3 discusses our modeling of undefined behavior (which we use to formally specify value range analysis). Finally, §4.4 describes certain trade-offs in our model.

## 4.1 Capped Memory

We note that PS's certification against every memory extension is quantifying over two aspects of possible interference: message *values* and message *views*.

We observe that quantifying only over message views suffices for DRF-RA. By carefully analyzing CDRF, we can see that for DRF-RA, one has to make sure that during the certification of promises, no *acquire-release RMW* reads from a message that already exists in the memory. Indeed, (i) due to interference by other threads, such RMW may not have the opportunity to read from that message in the actual run; and (ii) such racy RMWs may exist (the DRF-RA assumption does not prevent them). Together, (i) and (ii) invalidate the DRF-RA guarantee (as happens in CDRF). We observe here that this is the *only* role of the future memory quantification that is required for ensuring DRF-RA.

The conservative future memory quantification of PS indeed disallows such problematic RMWs during certification. In fact, even certification against memory extensions that do not introduce new values in the future memory suffices for DRF-RA. For example, in CDRF, when certifying against  $M_{\text{future}}$  that, in addition to the initialization messages, has a message form  $m = \langle x : 0@(0, \_], R \rangle$  with  $R(y) \geq t$ , thread 1 is forced to read m when performing its **FADD**. Since it is an acquire **FADD**, it will increase the thread view of y to R(y), which will not allow it to fulfill its promise. More

generally, when a thread promises a message of the form  $\langle x : v@(f,t],V \rangle$  in the current memory M, there is always a possible memory extension  $M_{\text{future}}$  of M that forces (non-promised) RMWs of location y performed during certification (which read from a message in  $M_{\text{future}}$ ) to read from a specific message  $m_{\text{future}}^y \in M_{\text{future}}$  whose view of x is greater than or equal to t. When such RMWs are acquire RMWs, this will force the thread to increase its view of x to at least t, which, in turn, does not allow the thread to fulfill its promise.

**Remark 1.** Completely disallowing release-acquire RMWs during certification is too strong. We should allow them to read from local writes added during certification, since no other thread can prevent them from doing so.

We further observe that value-range analysis concerns message *values*, but it is *insensitive* to message *views*. As we saw for the GA program above, the conservative future memory quantification of PS is doing too much: it forbids any promise that depends on the value read by an RMW, which invalidates value-range analysis. However, we note that there is no problem in disallowing the following variant of GA that uses an acquire CAS instead of a relaxed one:

Although value analysis may deduce that a < 10 is always true, it cannot justify the reordering of  $a := \mathbf{CAS}^{\mathsf{acq}}(x, 0, 1)$  and y := 1, since acquire accesses in general cannot be reordered with subsequent accesses. In other words, an analysis that is based solely of values does not give any information about the views of read messages, so that any optimization based on such analysis cannot enable reordering of acquire RMWs.

Based on these observations, it seems natural to replace the conservative future memory quantification of PS with a requirement to certify against all extensions of the current memory M that employ values that already exist in M (for each location). While this approach makes value-range analysis sound and maintains DRF-RA, it is still too strong for the combination of local and global optimizations. Indeed, consider the following variant of the GA+E program above.

$$x := 42$$

$$x := 0$$

$$f lag^{\text{rel}} := 1$$

$$| f := f lag$$

$$a := CAS^{\text{acq}}(x, 0, 1) \text{ // } 1$$

$$if a < 10 \text{ then}$$

$$y := 1$$

$$| GA+E^{\text{''}}$$

In order for thread 2 to promise y := 1, the write to flag has to be executed first. (Note that a release write cannot be promised.) Therefore, the value 42 for x exists in memory when the promise y := 1 is made, but, to support both the elimination of overwritten values and global value analysis, x := 42 should not be considered as a possible extension of

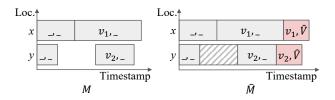

**Figure 1.** An example of the capped memory

the current memory. We observe that it is enough, however, to consider memory extensions whose additional messages *only* use values of maximal messages (which were not yet overwritten) to each location.

Now, instead of quantifying over a restricted set of memory extensions, we identify the most restrictive such extension, which we called the "capped memory". This leads to a conceptually simpler certification condition, where certification is needed only against one particular memory, which is uniquely determined by the current memory. The capped memory  $\widehat{M}$  of a memory M is obtained by:

- Filling all "gaps" between existing messages so that non-promised RMWs can only read from the maximal message of the relevant location. In other words, for every two messages  $m_1 = \langle x : @(\_, t], \_ \rangle$  and  $m_2 = \langle x : @(f, \_], \_ \rangle$  with t < f and no message in between, we block the space between t and f. (The exact mechanism to achieve this, "reservations", is discussed in §4.2.)

- For every location x, attaching a "cap message"  $\widehat{m}_x$  with a *globally maximal view* to the latest message to x in M:

$$\widehat{m}_x = \left\langle x : \widehat{v}_x@(\widehat{t}_x,\widehat{t}_x+1], \widehat{V}_M \right\rangle$$

where  $\hat{t}_x$  and  $\hat{v}_x$  are the "to"-timestamp and the value of the message to x in M with the maximal "to"-timestamp, and  $\hat{V}_M$  is given by:

$$\widehat{V}_M = \lambda y$$

. max{ $t \mid \langle y : @(\_, t], \_ \rangle \in M$ }.

Fig. 1 depicts an example of the capped memory construction. The shaded area in  $\widehat{M}$  represents the blocked space.

Starting from  $\widehat{M}$ , any (non-promised) RMWs reading from a message in  $\widehat{M}$  are forced to read from the  $\widehat{m}_x$  messages (since the timestamp interval  $[0,\widehat{t}_x]$  is completely occupied). Because these messages carry maximal views, acquire RMWs reading from them cannot be executed during certification, as it will increase the thread view to  $\widehat{V}_M$ , which, in turn, will prevent the thread from fulfilling its outstanding promises.

In turn, the new machine step is then simplified as follows:

$$\frac{\langle \mathcal{TS}(i), M \rangle \to^+ \langle \mathit{TS}', M' \rangle}{\exists \mathit{TS}''. \langle \mathit{TS}', \widehat{M'} \rangle \to^* \langle \mathit{TS}'', \_ \rangle \wedge \mathit{TS}''. \mathsf{prm} = \emptyset}{\langle \mathcal{TS}, M \rangle \to \langle \mathcal{TS}[i \mapsto \mathit{TS}'], M' \rangle}$$

Since the capped memory is clearly one possible future memory, the semantics we obtain is clearly weaker than PS. It is (i) weak enough to allow the annotated behaviors of GA and RP above: certification against the capped memory will not lead to  $a \ge 10$  in GA and to  $c \ne 0$  in RP; and, on the other hand, (ii) strong enough to forbid the annotated behavior of CDRF above: certification against the capped memory will not allow the y := 1 promise. In particular, by using the maximal messages for constructing capped memory, thread 2 of GA+E' can promise y := 1 and certify it while the message x := 42 (which is overwritten by x := 0) is in the memory.

**Remark 2.** The original PS quantification over all future memories could equivalently quantify over all memories defined just like the capped memory, except for using arbitrary values for the cap messages. Capped memory is more than that: it sets the value of each cap messages to that of the corresponding maximal message.

#### 4.2 Reservations

While capped memory suffices for justifying the weak outcomes of the examples seen so far, it is still too strong to support register promotion and to validate the intended mapping to ARMv8. Consider the following variant of RP that uses an *acquire* RMW in thread 1.

$$a := x //1$$

$c := \mathbf{FADD}^{\mathsf{acq}}(z, a) //0$

$y := 1$

$b := y //1$

$x := b$

(RPacq)

The weakening of PS presented in §4.1 disallows the annotated behavior. Thread 1 cannot promise y:=1 because its certification has to execute a non-promised *acquire* RMW reading from an existing message against the capped memory; and also it cannot promise the RMW z:=1 before y:=1 because its certification requires reading x:=1. Nevertheless, as for RP, a global analysis may notice that z is accessed only by one thread and perform register promotion, yielding the annotated outcome. (Similarly, ARMv8 allows the annotated behavior of the corresponding target program.)

We note that the standard (Java) optimization of removing locks used by only one thread requires to perform register promotion on local locations accessed by acquire RMWs. Indeed, lock acquisitions are essentially acquire RMWs.

So, how can we allow such behaviors without harming DRF-RA? Our idea here is to enhance PS by allowing one to declare which thread will win the competition to perform an RMW reading from a given message m. Once such a declaration is made, RMWs performed by other threads cannot read from m.

The technical mechanism for these declarations is simple: we add a "reservation" step to PS, allowing a thread to reserve a timestamp interval that it plans to use later, without committing on how it will use it (what value and view will be picked). Once an interval is reserved, other threads are blocked from reusing timestamps in this interval. Intuitively, a reservation corresponds to promising the "read part" of the RMW, which confines the behavior of other threads. In particular, if a thread reserves an interval  $(t_1, t_2]$  attached to

some message  $(f, t_1]$ , then other threads cannot read from the  $(f, t_1]$  message with an RMW operation.

Since reservations are included in the machine memory (just like normal writes and promises), the semantics remains thread-local. Technically, reservations take the form  $\langle x:(f,t]\rangle$  where  $x\in \text{Loc}$  and (f,t] is a timestamp interval. To meet their purpose, we allow attaching reservations only immediately after existing concrete messages (f should be the "to"-timestamp of some existing message to the same location). Threads are also allowed to cancel their reservations (provided they can still certify their outstanding promises) if they no longer need to block an interval. This is technically needed for the soundness of register promotion (see [1, §B]).

Returning to the RPacq program above, reservations allow the annotated outcome. Thread 1 can first reserve the interval (0,1] for z. Then, it can promise y:=1 and certify its promise by using its own reservation to perform the RMW.

Intuitively, reservations are closer to the implementation of RMWs in ARM: reserving the read part of an RMW first and then writing the RMW at the reserved space later corresponds to execution of a load exclusive first and a (successful) write exclusive later.

Reservations are also used in the definition of the capped memory to fill the gaps between messages to the same location (§4.1). In the presence of reservations, however, the capped memory definition requires some care. First, the value of the cap messages  $\widehat{m}_x$  should be the value of the maximal concrete message to x (reservations do not carry values). Second, when constructing the capped memory for thread i, if the maximal message to some location y is a reservation of thread i itself, then we do not add a cap message for y. In effect, during certification, the thread can execute any RMW on y but only after filling the reserved space on y. Other threads cannot execute an RMW on reservations of thread i, and so cannot interfere with respect to y.

#### 4.3 Undefined Behavior

So far, we have described value-range optimizations by informally referring to a global analysis performed by the compiler. For our formal development, we introduce *undefined behavior* (UB). We note that UB, which is not supported in the original PS model, is also useful in a broader context (*e.g.*, to give sensible semantics to expressions like x/0).

In order to formally define global optimizations, we include in our language an abort instruction, **abort**, which causes UB. In turn, for a global invariant I (formally defined in §6.2), we allow the program transformation introducing at arbitrary program points the instruction **assert**(I), which is a syntactic sugar to **if**  $\neg I$  **then abort**. This paves the way to further *local* optimizations, such as:

$$\begin{array}{ll} \mathbf{assert}(x \in \{0,1\}) \\ a := x \\ \mathbf{if} \ a \in \{0,1\} \ \mathbf{then} \ c \end{array} \qquad \begin{array}{l} a := x \\ c \end{array}$$

The standard semantics of UB is "catch-fire": UB should be thought as allowing any arbitrary sequence of operations. This enables common compiler optimizations (*e.g.*, **if** e **then** c **else abort**  $\rightarrow$  c). Nevertheless, to make sure the semantics is not overly weak, like any thread step, for taking an **abort**-step, the certification condition has to be satisfied (where the certifying thread may replace **abort** by any sequence of operations).

Our formal condition for taking an **abort**-step is somewhat simpler: we require that for every location x, the current view of the aborting thread for x should be lower than the "to"-timestamp of all the outstanding promises for x of that thread. We say a thread is *promise-consistent* when this condition is met. Recall that a thread can take a write step to a location x when the thread view of x is lower than the "to"-timestamp of the writing message. In turn, considering that taking an **abort**-step is capable of executing arbitrary write instructions, a thread is able to fulfill its outstanding promises when aborting if and only if it is promise-consistent.

#### 4.4 Relaxed RMWs in Certifications

In PS 2.0, we opted to allow relaxed RMWs (that were non-promised before and read from a message that exists in the current memory) during certification of promises. This design choice can cause execution deadlocks:

$$a := \mathbf{FADD}(x, 1) //0$$

$y := 1 + a$   $b := \mathbf{FADD}(x, 1)$  (deadlock)

Suppose that in the beginning of the run the thread 1 promises y := 1. This promise can be certified against the capped memory by reading from the cap message of x (whose value is 0). Now, thread 2 can perform its RMW, and block thread 1 from fulfilling its promise. Although allowing such deadlocks is awkward, they are inconsequential, since deadlocking runs are discarded from the definition of observable behavior.

Similarly, this choice enables somewhat dubious behaviors that seem to invalidate atomicity of relaxed RMWs: for instance, CDRF can have the annotated behavior if one **FADD** is made rlx. Such behaviors are actually unavoidable if one insists on allowing all (local and global) optimizations allowed by PS 2.0 ([1, §C] provides an example).

A stronger alternative would be to disallow relaxed RMWs during certification unless they were promised before the certification, or they read from a message that is added to the memory during certification. This can be easily achieved by defining the capped memory (against which threads certify their promises) to include a reservation instead of a cap message, which disallows to read from cap messages during certification. The resulting model is deadlock-free and it supports all (global and local) optimizations supported by PS 2.0, except for the local reordering of a relaxed RMW followed by a write. To see this consider the following example:

$$a := \mathbf{FADD}(x, 1) \ // 1 \ || \ b := y \ // 1 \ y := 1 \ (LB-RMW)$$

To read the annotated values, the run must start with thread 1 promising y := 1. Such a promise can only be certified if we allow relaxed RMWs that read an existing message during certification. Nevertheless, reordering the two instructions in thread 1 clearly exhibits the annotated behavior. In particular, since ARMv8 performs such reorderings, the mapping to ARMv8 should always include a dependency from relaxed RMWs, thereby incurring some (probably small) overhead.

## 5 Formal Model

In this section, we present our formal model, called PS 2.0, which combines and makes precise the ideas outlined above. For simplicity, we omit some features that were included in PS (plain accesses, fences, release sequences, and split and lower of promises).<sup>7</sup> All of these features are handled just like in PS and are included in our Coq formalization. The full operational semantics and the programming language are presented in [1, §A].

To keep the presentation simple and abstract, we do not fix a particular programming language syntax, and rather assume that the thread semantics is already provided as a labeled transition system, with transition labels Silent for a silent thread transition with no memory effect, R(o,x,v) for reads, W(o,x,v) for writes,  $U(o_r,o_w,x,v_r,v_w)$  for RMWs, Fail for failing assertions, Sys(v) for a system calls.

The o, o<sub>r</sub>, o<sub>w</sub> variables denote access modes, which can be either rlx or ra. We use ra for both release and acquire, and include two access modes in RMW labels: a read mode and a write mode. These naturally encode the syntax of the examples we discussed above, e.g.,

$$\begin{split} \mathbf{FADD} & \to \mathtt{U}(\mathtt{rlx},\mathtt{rlx},...) & \mathbf{FADD}^\mathtt{acq} & \to \mathtt{U}(\mathtt{ra},\mathtt{rlx},...) \\ \mathbf{FADD}^\mathtt{acqrel} & \to \mathtt{U}(\mathtt{ra},\mathtt{ra},...) & \mathbf{FADD}^\mathtt{rel} & \to \mathtt{U}(\mathtt{rlx},\mathtt{ra},...) \end{split}$$

Next, we present the components of the PS 2.0 model.

*Time.* Time is a set of *timestamps* that is totally and densely ordered by < with a minimum value, denoted by 0.

*Views.* A *view* is a function V: View  $\triangleq$  Loc  $\rightarrow$  Time. We use  $\bot$  and  $\sqcup$  to denote the natural bottom elements and join operations for views (pointwise extensions of the timestamp 0 and max operation on timestamps).

**Concrete Messages.** A concrete message takes the form  $m = \langle x : v @ (f, t], R \rangle$  where  $x \in \mathsf{Loc}, v \in \mathsf{Val}, f, t \in \mathsf{Time},$  and  $R \in \mathsf{View}$ , such that f < t or f = t = 0, and  $R(x) \le t$ . We denote by  $m.\mathsf{loc}, m.\mathsf{val}, m.\mathsf{from}, m.\mathsf{to},$  and  $m.\mathsf{view}$  the components of m.

**Reservations.** A reservation takes the form  $m = \langle x : (f, t] \rangle$ , where  $x \in \text{Loc}$ , and  $f, t \in \text{Time}$  such that f < t. We denote by m.loc, m.from, and m.to the components of m.

**Messages.** A message is either a concrete message or a reservation. Two messages  $m_1$  and  $m_2$  are disjoint, denoted by  $m_1 \# m_2$ , if they have different locations or disjoint timestamp intervals:

$$m_1 \# m_2 \triangleq m_1.1$$

oc  $\neq m_2.1$ oc  $\vee$

$m_1.$ to  $< m_2.$ from  $\vee m_2.$ to  $< m_1.$ from

Two sets  $M_1$  and  $M_2$  of messages are disjoint, denoted by  $M_1 \# M_2$ , if  $m_1 \# m_2$  for every  $m_1 \in M_1$  and  $m_2 \in M_2$ .

**Memory.** A memory is a (nonempty) pairwise disjoint finite set of messages. We write M(x) for the sub-memory  $\{m \in M \mid m. loc = x\}$  and  $\widetilde{M}$  for the set  $\{m \in M \mid m = \langle \_: @(\_, \_], \_ \}$  of concrete messages in M.

*Memory Operations.* A memory M supports the *insertion* for a message m denoted by  $M \overset{\triangle}{\leftarrow} m$  and given by  $M \cup \{m\}$ . It is only defined if: (i)  $\{m\} \# M$ , (ii) if m is a concrete message with m.loc = x, then no message  $m' \in M(x)$  has m'.from = m.to, and (iii) if m is a reservation with m.loc = x, then there is some concrete message  $m' \in \widetilde{M}(x)$  such that m'.to = m.from. Note that the second condition enforces that once a message is not an RMW (*i.e.*, its "from"-timestamp is not attached to another message), it never becomes an RMW (*i.e.*, its "from"-timestamp remains detached). Technically, this condition is required for the soundness of the register promotion.

**Closed View.** Given a view V and a memory M, we write  $V \in M$  if, for every  $x \in \text{Loc}$ , we have V(x) = m.to for some concrete message  $m \in \widetilde{M}(x)$ .

**Thread States.** A thread state is a triple  $TS = \langle \sigma, V, P \rangle$ , where  $\sigma$  is a local state, V is a thread view, and P is a memory. We denote by TS.st, TS.view, and TS.prm the components of a thread state TS.

**Thread Configuration Steps.** A thread configuration is a pair  $\langle TS, M \rangle$ , where TS is a thread state and M is a memory. We use  $\bot$  as a thread configuration after a failure.

Fig. 2 presents the full list of thread configuration steps, which we discuss now. To avoid repetition, we use the helpers read-helper and write-helper. In these helpers,  $\{x@t\}$  denotes the view assigning t to x and 0 to other locations.

**PROMISE**. A thread can take a PROMISE-step by adding a concrete message m to the set of outstanding promises P and update the memory M to  $M \stackrel{\triangle}{\longleftarrow} m$ .

**RESERVE** and **CANCEL**. These two steps are specific to PS 2.0 model. In a reserve-step a thread reserves a timestamp interval by adding it to both the memory *M* and the set of outstanding promises *TS*.prm. The thread is allowed to drop the reservation from the set of outstanding promises and the memory using the CANCEL-step.

**READ.** In this step a thread reads the value of a location x from a message  $m \in M$  and extend its view. Following the READ-HELPER, the thread's view of location x is extended to

$<sup>^7</sup>$ In particular, note that the system calls in this simplified model do not enforce sequentially consistent fences.

**Memory Helpers:**

| (memory: new)                                                                                                                                                                                                                                           |                                                                                                                                                           |                                                                             | (WRITE-HELPER)                                                                                                                                                                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                         |                                                                                                                                                           |                                                                             | $m = \langle x : @(\_, t], R \rangle  V(x) < t$                                                                                                                                                               |

| $\langle P, M \rangle \xrightarrow{m} \langle P, M \xleftarrow{A} m \rangle$                                                                                                                                                                            | (READ-HELPER)                                                                                                                                             |                                                                             | $V' = V \sqcup \{x@t\}$ $o = r1x \Rightarrow R = \bot$                                                                                                                                                        |

|                                                                                                                                                                                                                                                         | $m = \langle x : @(\_, t], R \rangle$                                                                                                                     |                                                                             | $0 = \text{rix} \Rightarrow R = \bot$<br>$0 = \text{ra} \Rightarrow P(x) = \emptyset \land R = V'$                                                                                                            |

| (MEMORY: FULFILL)                                                                                                                                                                                                                                       | $o = rlx \Rightarrow V' =$                                                                                                                                | ( )                                                                         | N                                                                                                                                                                                                             |

| $m \in P$                                                                                                                                                                                                                                               | $o = ra \Rightarrow V' = V \sqcup \{x@t\} \sqcup R$                                                                                                       |                                                                             | $\langle P, M \rangle \xrightarrow{m} \langle P', M' \rangle$                                                                                                                                                 |

| $\langle P, M \rangle \xrightarrow{m} \langle P \setminus \{m\}, M \rangle$                                                                                                                                                                             | $\langle V, M \rangle \xrightarrow{o, m}_{\mathbf{R}} \langle V', M \rangle$                                                                              |                                                                             | $\langle V, P, M \rangle \xrightarrow{o, m}_{\mathbb{W}} \langle V', P', M' \rangle$                                                                                                                          |

| Thread Steps:                                                                                                                                                                                                                                           |                                                                                                                                                           |                                                                             |                                                                                                                                                                                                               |

| (PROMISE)                                                                                                                                                                                                                                               |                                                                                                                                                           |                                                                             |                                                                                                                                                                                                               |

| $m = \langle \_ : \_ @(\_, \_], R \rangle$                                                                                                                                                                                                              | (RESERVE)                                                                                                                                                 |                                                                             | (CANCEL)                                                                                                                                                                                                      |

| $M' = M \stackrel{A}{\hookleftarrow} m \qquad R \in M'$                                                                                                                                                                                                 | $m = \langle \_: (\_, \_] \rangle$                                                                                                                        | $M' = M \stackrel{A}{\hookleftarrow} m$                                     | $m = \langle \_: (\_, \_] \rangle \in P$                                                                                                                                                                      |

| $\overline{\langle\langle\sigma,\mathcal{V},P\rangle,M\rangle\rightarrow\langle\langle\sigma,\mathcal{V},P\cup\{m\}\rangle,}$                                                                                                                           | $\overline{M'}$ $\overline{\langle\langle\sigma,\mathcal{V},P\rangle,M\rangle\to\langle\langle\sigma,$                                                    | $\mathcal{V}, P \cup \{m\}\rangle, M'\rangle$                               | $(CANCEL)$ $m = \langle \_: (\_, \_] \rangle \in P$ $\langle \langle \sigma, \mathcal{V}, P \rangle, M \rangle \to \langle \langle \sigma, \mathcal{V}, P \setminus \{m\} \rangle, M \setminus \{m\} \rangle$ |

| (READ)                                                                                                                                                                                                                                                  | (WRITE)                                                                                                                                                   | (UPDATE)                                                                    |                                                                                                                                                                                                               |

| $\sigma \xrightarrow{\mathbb{R}(o,x,v)} \sigma'$                                                                                                                                                                                                        | $\sigma \xrightarrow{W(o,x,v)} \sigma'$                                                                                                                   |                                                                             | $\sigma \xrightarrow{U(o_{\mathrm{r}},o_{\mathrm{w}},x,\upsilon_{\mathrm{r}},\upsilon_{\mathrm{w}})} \sigma''$                                                                                                |

| $m = \langle x : v@(\_, \_], \_ \rangle$                                                                                                                                                                                                                | $m = \langle x : v@(\_, \_], \_ \rangle$                                                                                                                  | $m_r = \langle x :$                                                         | $v_{\mathrm{r}}@(\_,t],\_\rangle \qquad m_{\mathrm{w}}=\langle x:v_{\mathrm{w}}@(t,\_],\_\rangle$                                                                                                             |

|                                                                                                                                                                                                                                                         | $\langle V, P, M \rangle \xrightarrow{o, m}_{W} \langle V', P', M' \rangle$                                                                               | $\langle V, M \rangle \xrightarrow{o_{\rm r}, m_{\rm r}}_{\rm R}$           | $\langle V', M \rangle \qquad \langle V', P, M \rangle \xrightarrow{o_{w}, m_{w}} \langle V'', P'', M'' \rangle$                                                                                              |

| ${\langle\langle\sigma,V,P\rangle,M\rangle\to\langle\langle\sigma',V',P\rangle,M\rangle}$                                                                                                                                                               |                                                                                                                                                           |                                                                             | $\langle \sigma, V, P \rangle, M \rangle \rightarrow \langle \langle \sigma'', V'', P'' \rangle, M'' \rangle$                                                                                                 |

| (SILENT)                                                                                                                                                                                                                                                | (SYSTEM CALL)                                                                                                                                             | (1                                                                          | failure)                                                                                                                                                                                                      |

| $\sigma \xrightarrow{\text{Silent}} \sigma'$                                                                                                                                                                                                            | $\sigma \xrightarrow{\operatorname{Sys}(v)} \sigma'$                                                                                                      | ,                                                                           | $\sigma \xrightarrow{\mathtt{Fail}} \bot \qquad \langle \sigma, \mathcal{V}, P \rangle$ is promise-consistent                                                                                                 |

| $\overline{\langle\langle\sigma,\mathcal{V},P\rangle,M\rangle \to \langle\langle\sigma',\mathcal{V},P\rangle,M\rangle}$                                                                                                                                 | $\langle \langle \sigma, \mathcal{V}, P \rangle, M \rangle \xrightarrow{\operatorname{Sys}(v)} \langle \langle \sigma, \mathcal{V}, P \rangle, M \rangle$ | $\sigma', \mathcal{V}, P \rangle, M \rangle$                                | $\langle\langle\sigma,\mathcal{V},P\rangle,M angle \xrightarrow{\mathtt{Fail}} \bot$                                                                                                                          |

| Machine Steps:                                                                                                                                                                                                                                          |                                                                                                                                                           |                                                                             |                                                                                                                                                                                                               |

| (                                                                                                                                                                                                                                                       | (MACHINE SYST                                                                                                                                             | гем call)                                                                   |                                                                                                                                                                                                               |

| (MACHINE NORMAL)                                                                                                                                                                                                                                        | M'\                                                                                                                                                       | $\rightarrow^* \xrightarrow{\operatorname{Sys}(v)} \langle TS', M' \rangle$ | (MACHINE FAIL)                                                                                                                                                                                                |

| $\langle \mathcal{TS}(i), M \rangle \to^+ \langle \mathcal{TS}', M' \rangle$ $\langle \mathcal{TS}(i), M \rangle \to^* \xrightarrow{Sys(\mathcal{V})} \langle \mathcal{TS}', M \rangle$ is consistent $\langle \mathcal{TS}', M' \rangle$ is consistent |                                                                                                                                                           | , , ,                                                                       | $\langle \mathcal{TS}(i), M \rangle \mathop{ ightarrow}^* \stackrel{\mathtt{Fail}}{\longmapsto} \bot$                                                                                                         |

|                                                                                                                                                                                                                                                         |                                                                                                                                                           |                                                                             | <del></del>                                                                                                                                                                                                   |

| $\langle \mathcal{TS}, M \rangle \to \langle \mathcal{TS}[i \mapsto TS]$                                                                                                                                                                                | $\langle \mathcal{TS}, M' \rangle \qquad \langle \mathcal{TS}, M \rangle \stackrel{\operatorname{Sys}(7)}{\longrightarrow}$                               | $\xrightarrow{\upsilon)} \langle \mathcal{TS}[i \mapsto TS'], M'$           | $\langle \mathcal{TS}, M \rangle \xrightarrow{Fail} \bot$                                                                                                                                                     |

Thread Helpers:

Figure 2. Formal operational semantics

timestamp t. When the read is an acquire read, the view is also updated by the message view R.

**WRITE** and **UPDATE**. The write and the update steps cover two cases: a fresh write to memory (MEMORY:NEW) and a fulfillment of an outstanding promise (MEMORY:FULFILL). When a thread writes a message m with location x along with timestamp  $(\_, t]$ , t extends the thread's view of location x to memory M. A release write step additionally ensures that the thread has no outstanding promise on location x. Moreover, a release write attaches the updated thread view V' to the message m. The update step is similar, except that it first reads a message with a timestamp interval  $(\_, t]$ , and then, writes a message with an interval  $(t, \_]$ .

**SILENT**. A thread takes a SILENT-step to perform thread-local computation which updates only the local thread state.

**SYSTEM CALL**. A thread takes a SYSTEM CALL-step that emits an event with the call's input and output values.

**FAILURE**. We only allow a thread configuration  $\langle TS, M \rangle$  to fail if TS is *promise-consistent*:

$$\forall m \in \mathit{TS}.\mathsf{prm}, \mathit{TS}.\mathsf{view}(m.\mathsf{loc}) \leq m.\mathsf{to}$$

*Cap View and Messages.* The last message of a memory M to a location x, denoted by  $\overline{m}_{M,x}$ , is given by:

$$\overline{m}_{M,x} \triangleq \underset{m \in M(x)}{\operatorname{arg max}} m.\mathsf{to}$$

The *cap view* of a memory M, denoted by  $\widehat{V}_M$ , is given by:

$$\widehat{V}_{M} \triangleq \lambda x. \ \overline{m}_{\widetilde{M},x}.$$

to

By definition, we have  $\widehat{V}_M \in M$ . The *cap message* of a memory M to a location x, denoted by  $\widehat{m}_{M,x}$ , is given by:

$$\widehat{m}_{M,x} = \langle x: \overline{m}_{\widetilde{M},x}. \mathtt{val}@(\overline{m}_{M,x}. \mathtt{to}, \overline{m}_{M,x}. \mathtt{to} + 1], \widehat{V}_{M} \rangle$$

**Capped Memory.** The capped memory of a memory M with respect to a set of promises P, denoted by  $\widehat{M}_P$ , is an extension of M, constructed in two steps:

- 1. For every  $m_1, m_2 \in M$  with  $m_1.loc = m_2.loc, m_1.to < m_2.to$ , and there is no message  $m' \in M(m_1.loc)$  such that  $m_1.to < m'.to < m_2.to$ , we include a reservation  $\langle m_1.loc : (m_1.to, m_2.from] \rangle$  to  $\widehat{M}_P$ .