# **VeriRT: An End-to-End Verification Framework for Real-Time Distributed Systems**

YOONSEUNG KIM, Seoul National University, South Korea and Yale University, USA SUNG-HWAN LEE\*, Seoul National University, South Korea YONGHYUN KIM, Seoul National University, South Korea CHUNG-KIL HUR, Seoul National University, South Korea

Safety-critical systems are often designed as real-time distributed systems. Despite the need for strong guarantees of safety and reliability in these systems, applying formal verification methods to real-time distributed systems at the implementation level has faced significant technical challenges.

In this paper, we present VeriRT, an end-to-end formal verification framework that closes the formal gap between high-level abstract timed specifications and low-level implementations for real-time distributed systems. Within the framework, we establish a theoretical foundation for constructing formal timed operational semantics by integrating conventional operational semantics and low-level timing assumptions, along with principles for reasoning about their timed behaviors against abstract specifications. We leverage CompCert's correctness proofs to guarantee the correctness of the assembly implementation of real-time distributed systems. We provide two case studies on realistic real-time systems. All the results are formalized in Coq.

CCS Concepts: • Theory of computation  $\rightarrow$  Operational semantics; Program verification; Distributed computing models; • Computer systems organization  $\rightarrow$  Real-time system specification.

Additional Key Words and Phrases: formal verification, real-time systems, distributed systems, refinement

#### **ACM Reference Format:**

Yoonseung Kim, Sung-Hwan Lee, Yonghyun Kim, and Chung-Kil Hur. 2025. VeriRT: An End-to-End Verification Framework for Real-Time Distributed Systems. *Proc. ACM Program. Lang.* 9, POPL, Article 61 (January 2025), 28 pages. https://doi.org/10.1145/3704897

## 1 Introduction

Safety-critical systems, where ensuring safety and reliability is the top-priority task, are often designed as real-time distributed systems. Examples include autonomous vehicle systems, avionics systems, and nuclear systems [Chen et al. 2017; Gawand et al. 2017; Sampigethaya and Poovendran 2012], whose reliability critically depends on the prompt detection of environmental changes and timely responses. Moreover, they fall under the category of cyber-physical systems, where many of which adopt a distributed design to accommodate physical limitations [Khaitan and McCalley 2015; Shi et al. 2011].

However, applying formal verification methods directly to real-time distributed systems to achieve a high level of reliability poses considerable technical challenges. Even the verification of

Authors' Contact Information: Yoonseung Kim, Seoul National University, Seoul, South Korea and Yale University, New Haven, USA, yoonseung.kim@yale.edu; Sung-Hwan Lee, Seoul National University, Seoul, South Korea, sunghwan.lee@sf.snu.ac.kr; Yonghyun Kim, Seoul National University, Seoul, South Korea, yonghyun.kim@sf.snu.ac.kr; Chung-Kil Hur, Seoul National University, Seoul, South Korea, gil.hur@sf.snu.ac.kr.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for third-party components of this work must be honored. For all other uses, contact the owner/author(s).

© 2025 Copyright held by the owner/author(s).

ACM 2475-1421/2025/1-ART61

https://doi.org/10.1145/3704897

<sup>\*</sup>Now at Rebellions Inc.

non-real-time distributed systems [Drăgoi et al. 2016; Hawblitzel et al. 2015; Honoré et al. 2021; Sergey et al. 2017; v. Gleissenthall et al. 2019; Wilcox et al. 2015] using conventional methods is acknowledged to be challenging, as it involves proving system-wide invariants under arbitrary interleavings of distributed nodes. Furthermore, verifying real-time systems necessitates quantitative reasoning about the specific timings of observable events, a requirement not supported by conventional methods that represent timing information for events in an abstract sequential order.

In our attempt to develop a new foundation for the real-time distributed system verification, we have faced the following challenges:

Modeling Timed Behaviors. In traditional approaches that only consider sequences of events without precise timing, the language semantics of a program (whether at the source, machine, or specification level) fully determines the sequence of observable events. However, when timing is introduced, defining program semantics that accurately predict the timing of each event becomes challenging. This difficulty arises because while compilers are expected to maintain the order of observable events from source to target code, they are not required to preserve exact timing. In fact, compiler optimizations typically aim to reduce execution time, which inevitably alters the timing of events. This discrepancy complicates the development of a semantic model that can reliably predict the timing of events in optimized code.

Quantitative Reasoning about Timing. The correctness of real-time systems hinges on both their computational behavior and timing characteristics, creating an intrinsic interdependence in correctness reasoning. To illustrate this, consider a system that launches tasks at regular intervals using a system call like sleep. A computational bug leading to an incorrect calculation of the sleep duration could result in job launches deviating from the specified timing (i.e., a timing bug). Conversely, a delayed job launch (i.e., a timing bug) might cause a message to be transmitted to another node too late, potentially disrupting the entire system's functionality (manifesting as a computational bug). Thus, we require a well-crafted verification technique that enables quantitative reasoning about both timing and computational behaviors in tandem.

Complexities Arising from Distributed Computation. Verifying distributed systems presents additional challenges due to an inherently high degree of nondeterminism. Three main factors contribute to this complexity: (i) real-time interleaving of operations across physical nodes comprising the system, (ii) each node's local clock exhibiting randomly varying skew, and (iii) message exchanges between nodes subject to random delays, drops, or duplications. To ensure the overall system's correctness, we first need a distributed system model that conservatively captures all possible behaviors arising from these sources of nondeterminism. Furthermore, we need reasoning principles that allow us to effectively manage this complex nondeterminism across multiple nodes.

In this paper, we present VeriRT, a novel formal verification framework for real-time distributed systems, addressing these challenges with the following features.

First, we develop a novel theory for modeling the timed behaviors of programs. In our approach, we treat the timing of events differently from the ordering of events. While the ordering is determined by the semantics of a program at different levels, the timing is only determined by the actual machine code running on hardware. Therefore, unlike the ordering of events, we allow users to specify timing conditions for observable events generated by the actual machine code, which is set out as a separate verification condition that should be externally validated via empirical methods or worst-case execution time (WCET) analyses against the compiled machine code. Then, we reflect these timing conditions in higher-level operational semantics in the form of timing assumptions. For this, we develop the notion of *timed operational semantics* that combines conventional untimed

operational semantics with user-specified timing assumptions, generating observable behaviors in the form of a sequence of *timed events*. It is important to note that imposing timing assumptions in high-level operational semantics is necessary because computational behaviors can depend on these timing assumptions, as discussed earlier.

Second, we develop proof techniques for reasoning about the timed behaviors of programs. For this, we introduce *timed simulation relations* that enable timing-sensitive reasoning to prove behavioral refinement between the timed behaviors of two programs. Moreover, we provide a lifting theorem that allows for timing-insensitive reasoning: given a conventional simulation proof between (untimed) behaviors of two programs, we can lift this simulation into a timed simulation between their timed behaviors with the same timing assumptions. This timing-insensitive reasoning is typically applied to compiler verification, in our work specifically for CompCert [Leroy 2009a], a realistic C compiler formally verified in Coq.

Third, to address the challenge regarding distributedness, our framework supports specifying and reasoning about the behavior of local clocks and the network. Specifically, our distributed system model assumes a virtual global clock as a reference, allowing users to specify the behavior of local clocks in relation to this global clock. In our case studies, we consider two different specifications of local clock behavior. For the network, users can adjust a set of parameters to express various assumptions regarding its behavior. The framework then provides *node-local* and *global* timed simulations as proof techniques to resolve nondeterminism. Node-local simulation facilitates abstraction of node-local timed behavior, including the local clock, while global simulation can be applied to deal with interleavings and network behavior. It is important to note that the assumptions about local clock and network behaviors form part of our trust base and are subject to external validation.

This paper includes two case studies that demonstrate the application of VeriRT. In the first case study, we implement and verify a well-known clock synchronization mechanism called Cristian's algorithm. We verify that the clock skews are bounded within the specified range under appropriate assumptions about the local clock's hardware behavior. The second case study presents a simplified implementation of real-time system middleware called PALSware, which provides a logically synchronous environment to applications built on top of a physically asynchronous network. We verify the correctness of this PALSware implementation under appropriate assumptions about the local clock and network behavior.

Additionally, we prove that the entire transformation chain of CompCert 3.9 preserves our timed operational semantics from the C level down to the assembly level. We prove that the generic simulation relation of CompCert also establishes refinement under our timed operational semantics, thanks to the aforementioned lifting theorem. This extension of CompCert's correctness proofs to our timed semantics is packaged as CompCertRT within our framework. Consequently, CompCertRT enables end-to-end verification from an abstract specification down to a final executable.

All results are formalized in Coq.

The remainder of the paper is organized as follows: §2 provides an overview of the theoretical foundation of VeriRT and outlines the overall structure of the framework. §3 introduces our formalism for representing real-time distributed systems, timed behaviors, and refinement. §4 offers a detailed explanation of the formal distributed system model, including our models for the network and operating systems. §5 presents the proof techniques offered by VeriRT and the rationale behind their designs. §6 describes the construction of CompCertRT, an integration of CompCert within our framework. §7 and §8 present two case studies illustrating the practical application of the framework. §9 evaluates our development. Finally, §10 concludes the paper by comparing our work with existing studies.

#### 2 Overview

This section introduces the core concept underlying our theory for modeling and reasoning about timed behaviors of programs. We illustrate this concept with an example program that operates under real-time constraints. Next, we present the structure of Veriret, a formal verification framework for real-time distributed systems, built upon this theoretical foundation.

# 2.1 Modeling Timed Behaviors of Programs

*Ordered Events vs. Timed Events*. Program semantics define observable behaviors, each comprising events such as I/O operations with associated timings. Traditional approaches typically represent these timings as a sequential order of events, without specifying exact times. However, for real-time system verification, we cannot abstract away precise timings, as such verification demands quantitative reasoning about when events occur.

Let's first review traditional approaches to semantics with ordered events. In these approaches, language semantics can be designed as an abstract state machine. This machine processes a given program step by step, generating observable events in a sequential order. Here, a program serves as a standalone representation for the operational semantics. Compilers can legitimately transform these programs into various representations, provided they maintain the original order of events.

However, the traditional approaches face challenges when addressing timed operational semantics — semantics that generate events with precise timing values. Consider, for example, designing a standalone timed operational semantics for C (such as assigning an execution time bound for each command). In this scenario, ensuring compiler correctness would require preserving not only the order of events but also their precise timings. This approach presents technical difficulties in compiler development and doesn't align with how realistic compilers function. Compilers typically aim to reduce execution time or, in some cases, extend it for specific purposes (e.g., security or file size optimization). It's widely recognized that source programs are only loosely connected to actual execution time (e.g., time complexity). Consequently, the verification of precise time constraints must occur at the machine level, involving compiled executables and the target machine.

Our Approach to Modeling Timing. To construct a timed operational semantics, our method requires the user to provide timing assumptions for a program. These assumptions consist of time constraints regarding the interactions between the program and its environment (*i.e.*, invocations and returns of system calls). We then form a timed operational semantics by integrating these timing assumptions with the existing (untimed) operational semantics.

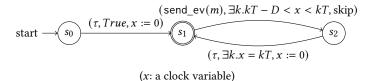

Fig. 1 illustrates an example program with its abstract specification. The system's primary task is to send a message periodically at a specified time. Each iteration involves two steps: first, computing a message (a process that may consume time), and then initiating message transmission within the time interval (kT - D, kT). Here, T represents a particular period, D(< T) is a given constant, and k is any integer. Such constraints are typical in time-division multiplexing where communication channels are allocated specific time slots.

Fig. 1a presents the abstract specification of this process as a timed automaton [Alur and Dill 1994]. Each edge is labeled with a triple (e, C, U) where e is an observable event, C is a condition for the transition to occur, and U is an operation that updates the clock variables after the transition. The process begins at  $s_0$  and may transition to  $s_1$  at any moment, resetting a clock x. While at  $s_1$ , the system may emit an event send\_ev(m) when the clock x is within a specified time interval. For simplicity, the specification disregards the message content. After sending a message, the system can return to  $s_1$ , resetting x to 0 when its value becomes a multiple of T, ensuring the next iteration follows the correct periodic schedule. The automaton accepts any observable behavior generated by an infinite transition sequence that indefinitely visits  $s_1$  (a Büchi condition).

(a) Automata specification

```

void main_loop() {

1

while (true) {

2

Msg m = compute_msg();

3

Int t_cur = get_time(); /** (a1,r1,s1,e1) |= [SC: 0<=e1-s1<Egt /\ s1<=r1<=e1] [WCET: s2-e1<E1] */

Int t_send = ((t_cur / T) + 1) * T - E;</pre>

5

6

if (t_send < t_cur)</pre>

t_send += T;

8

9

Int t_sleep = t_send - t_cur;

10

/** (a2,r2,s2,e2) |= [SC: a2<=e2-s2<a2+Esleep] [WCET: s3-e2<E2]

sleep(t_sleep);

11

12

13

send(m);

/** (a3,r3,s3,e3) |= [SC: 0<=e3-s3<Esend] [WCET: True]

*/

14

}

}

15

```

(b) C implementation

Fig. 1. Specification and implementation of a periodic process

Fig. 1b presents a C function main\_loop that implements the process. Let's first examine the code, disregarding comments. The function enters a loop and begins by computing a message via compute\_msg (whose detailed behavior is not relevant for this example). It then obtains the current local clock value t\_cur from the system call get\_time. Next, it calculates  $k = ((t_cur / T) + 1)$  and computes t\_send = kT - E (to be explained later) as the initial candidate time to start sending the message. If kT occurs too soon, rendering t\_send earlier than t\_cur, the function may need to wait another period T. It then calls the system call sleep to pause execution until t\_send, and finally sends the message through send(m). We consider the event send\_ev(m) to occur between the invocation and return of send(m).

Now, we explain how we define the timing assumptions. We use annotations of the form (a,r,s,e) |= [SC: C1] [WCET: C2] to clearly present time constraints associated with a system call. The variables (a,r,s,e) denote the argument, return value, start time, and end time of the associated system call for each invocation, respectively. Users can provide two types of constraints: the SC constraint imposed on the system call itself, and the WCET constraint on the code between system calls. In the WCET constraint, users may reference variables declared in constraints of other system calls. Importantly, these constraints are expressed relative to the local clock. Here, we assume a value  $\varepsilon$  as the maximum clock skew between the local and global clocks<sup>1</sup>.

In this example, we have three sets of constraints associated with get\_time, sleep, and send. For get\_time, the SC constraint specifies that the system call's execution time is bounded by Egt, and the return value must fall between the start and end times. The WCET constraint requires that the subsequent sleep system call invocation occurs within E1 time after get\_time returns. This means that the intermediate steps, including t\_send and t\_sleep computations, must complete within E1. For sleep, the SC constraint mandates that the blocking time is at least the given argument, with the call returning within Esleep. Its WCET constraint limits the time between sleep and send (involving no C commands in the source code) to at most E2. Lastly, the SC constraint for send

<sup>&</sup>lt;sup>1</sup>VeriRT may support different forms of assumptions on the local clock, as we explain in the case studies.

Fig. 2. Timed transition rules

specifies a maximum execution time of Esend. We do not impose any WCET condition between send and the subsequent get\_time.

*Construction of Timed Operational Semantics*. We now present the generic construction of timed operational semantics shown in Fig. 2, explaining it in two steps.

First, our approach transforms each transition  $s \xrightarrow{e} s'$  from the underlying untimed semantics into a timed transition  $(t,s) \xrightarrow{(t,e)} (t',s')$ , generating a timed event at time t and accounting for time passage until the next transition at  $t' \ge t$ . In this framework, we discretize time into extremely small units (e.g.,  $10^{-15}$  seconds), parameterized in our formalization, allowing us to model a transition step for each time unit. We introduce a latency state lat to represent the physical time required before the next transition occurs. Two key rules govern this process: the LATENCY rule, which decreases lat by one per step, generating a silent event  $\tau$ ; and the Progress rule, which captures the state transition when lat reaches zero, represented as  $s \xrightarrow{e} s'$ . After a Progress step, a new latency lat' is nondeterministically assigned. Importantly,  $s \xrightarrow{e} s'$  allows for multiple silent steps to occur along with a single, possibly non-silent event e, a feature particularly useful for maintaining conciseness in our theory (see §4.2 for more details).

Second, to eliminate executions that violate the timing assumptions, we augment the state with two elements: an event trace tr and a timeout point to. Initially, to is set to  $\infty$ . As events occur, the  $\mathcal T$  function, which encodes the timing assumptions, may update the timeout point. For instance, if tr and the current event e indicate a return from  $\mathtt{get\_time}()$  at Line 5 of our example program, to' is updated to  $t+\mathsf{E1}$ . The system can take arbitrary timed steps following the LATENCY and Progress rules until t reaches to. If t does reach to, the program generates a special no-behavior event, marking the execution as "invalid" (this is the TimeViolation rule). As an example, if the execution time exceeds  $\mathsf{E1}$  after returning from  $\mathsf{get\_time}$  without reaching sleep, the semantics generates a no-behavior event. When defining the system's observable behaviors, we discard these invalid executions. This approach assumes that the timing assumptions will be validated against the final executable (see §3 for details). For simplicity in this explanation, we have not distinguished between local and global clocks. This distinction will be addressed in detail in §4.

# 2.2 Reasoning about Timed Behaviors

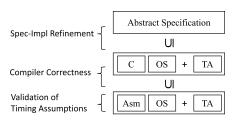

For a single program, the end-to-end verification from an abstract specification to the machine-level timed behavior comprises three layers, as illustrated in Fig. 3:

- Refinement proof: This layer establishes the relationship between the C implementation (including OS interactions) and the abstract specification.

- Compiler correctness: This layer ensures that the compiled code preserves the timed operational semantics of the source program.

Fig. 3. Verification layers of a single program

• Timing assumption validation: This layer confirms that the user-defined timing assumptions are satisfied by the actual machine-level execution.

Of the three layers, the framework directly provides the middle one concerning compiler correctness. A key theorem of VeriRT guarantees that when CompCert compiles a C program to an assembly program, the C program with its timing assumptions is refined by the resulting assembly program with the identical timing assumptions. The timing assumptions are designed to be independent of the underlying untimed operational semantics. This independence allows us to reuse CompCert's existing per-pass simulation proofs by applying our *lifting theorem*. We will present the details of this lifting theorem in §5 and our work on applying it to CompCert 3.9 in §6.

The user's responsibility for reasoning about timed behaviors is divided into two distinct tasks, represented by the top and bottom layers respectively. We will illustrate each of these tasks using the example provided in Fig. 1 in the following paragraphs.

Refinement between Specification and Implementation. The verification process linking the abstract specification to the C implementation necessitates combined reasoning about both the code's computational behaviors and the timing assumptions. Consider a scenario where the developer inadvertently introduces an error in Fig. 1b, causing the computation of t\_sleep to result in either an excessively short or long sleep duration. In a traditional approach using ordered events to represent timings, such a mistake would go undetected during verification, as it wouldn't alter the event sequence. In contrast, our approach allows for the explicit expression of timings in the specification, enabling proper verification of real-time systems.

We now present the high-level reasoning for verifying our example. Our goal is to demonstrate that the implementation meets the timed automata specification (Fig. 1a), which defines the safe time range as  $\exists k.(kT-D,kT)$ . Specifically, we need to prove that every occurrence of \$3\$ and \$e3\$ falls within this range for some k. To establish this, we begin by assuming the following condition on E: Egt+E1+Esleep+E2+Esend+ $\varepsilon$  < E <  $D-\varepsilon$  This condition forms the basis of our refinement proof. It's important to note that during the verification process, we must prove this condition holds for the concrete values of all constants involved. Our reasoning process integrates three key elements: the code itself, the timing assumptions, and the clock skew of the local clock.  $^2$

To begin, we will establish a lower bound for the variable s3 within a single iteration of the main loop. By reasoning about the computational behaviors, we can obtain that  $t_cur < t_send$  and  $t_send = kT - E$  for some k. Then, we get a lower bound from the following steps:

```

s3 \ge e2 \ge a2 + s2 = (kT - E) - t_cur + s2 (from execution order, SC of sleep, and code)

\ge (kT - E) - e1 + s2 \ge kT - E (from SC of get time and execution order)

```

Then, considering the maximum skew  $\varepsilon$ , the earliest possible invocation of send in terms of the global clock must be at least  $kT - E - \varepsilon > kT - D$ .

Second, we obtain an upper bound of e3 for the same iteration as follows:

```

e3 < s3 + Esend < e2 + E2 + Esend \qquad (from SC of send and WCET of sleep) \\ < E2 + Esend + s2 + a2 + Esleep \qquad (from SC of sleep) \\ s2 + a2 < E1 + e1 + (t_send - t_cur) \qquad (from WCET of get_time and code) \\ < E1 + Egt + s1 + ((kT - E) - r1) \qquad (from SC of get_time) \\ \leq E1 + Egt + s1 + ((kT - E) - s1) \qquad (from SC of get_time) \\ = E1 + Egt + (kT - E)

```

Again, considering  $\varepsilon$ , the latest possible return time of send is at most e3 +  $\varepsilon$  < Egt + E1 + Esleep + E2 + Esend + (kT - E) +  $\varepsilon$  < kT. Hence the program with the timing assumptions refines the automata specification.

<sup>&</sup>lt;sup>2</sup>For distributed systems, we would also need to account for message delivery times.

Validation of Timing Assumptions. Timing assumptions should be validated against the compiled executable on the target hardware with respect to its local clock. This validation ensures that the timed behaviors of the assembly code, as defined by our timed operational semantics, encompass all possible physical behaviors. It's important to note that this validation process is conducted outside our framework, as it relies on hardware-specific factors not modeled within our system. Users have flexibility in choosing validation methods based on their required confidence level. Options include rigorous testing or the use of Worst-Case Execution Time (WCET) analysis tools. Some compositional WCET analyses [Leveque et al. 2011; Marref 2010; Maxim et al. 2017] may be particularly helpful, allowing users to validate constraints on system calls and user-written code separately, then combine these results.

## 2.3 Structure of the Framework

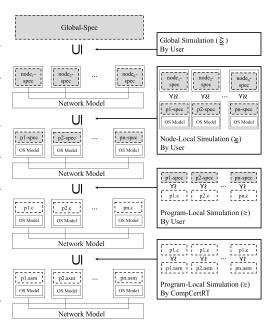

Building upon the theoretical foundation we have discussed, VeriRT enables the establishment of end-to-end refinement at the distributed system level, as illustrated in Fig. 4. The framework's most distinctive feature is its ability to divide the end-to-end verification process into multiple layers. This layered approach significantly simplifies the overall proof by allowing users to focus on reasoning about individual, local components within each layer. This modular verification strategy enhances both the manageability and scalability of the verification process for complex systems.

The verification process begins with the user constructing a formal model of the distributed system. This is achieved by writing programs in C language, which are represented as white dashed boxes in Fig. 4. Our framework then integrates these user-provided programs with its pre-built network and operating system models.

Fig. 4. Structure of the framework

This integration results in a comprehensive system that serves as the target for verification.

After constructing the formal model, the user proceeds with verification by building a series of refinement proofs. To facilitate this process, the user can define local specifications for individual system components, serving as intermediate steps in the verification. Our framework supports this approach by offering several simulation techniques that enable localized reasoning. In Fig. 4, we use gray shading to represent all specifications, illustrating the gradual abstraction process within our framework. The verification culminates in an end-to-end refinement, resulting from a vertical composition of the individual refinement proofs.

**Network and OS Models.** The network and OS models are designed to represent all possible behaviors of their real-world counterparts. For the network model, the user may control its behaviors by setting the model parameters  $\mu$  and  $\kappa$ , each denotes the maximum delivery time assumption and the maximum number of possible message duplication, respectively. The OS model contains the modeled behaviors of selected system calls, about local clock accesses, timers, and network sockets. The user may control the local clock's behavior by imposing a rule (*e.g.*, imposing the maximum clock skew bound). We will explain the two models in detail in §4.

**Refinement Layers**. The end-to-end verification shown in Fig. 4 is a composition of four refinement layers of proof. The framework provides three simulation relations as proof techniques: program-local, node-local, and global simulations. Global simulation is the most general one, and the other two are for reasoning about local components, which imply contextual refinement for the whole system. We will explain the proof techniques in §5. We summarize each layer along the bottom-up direction as follows.

- **Program Simulation by CompCertRT:** For any C programs given by the user, CompCertRT guarantees the program-local simulation between the C programs and their corresponding assembly programs compiled by itself. Program-local simulation is used to match the computational behavior of two programs. CompCertRT contains a generic proof that every translation of CompCert 3.9 satisfies program-local simulation, whose details will be presented in §6.

- **Program Simulation by User:** In this layer, the user provides a computational specification for each C program and proves program-local simulation to abstract away concrete details of the formal C operational semantics. The removal of the complex details helps the user to focus on reasoning about times in the above layers.

- Node-Local Simulation by User: This layer performs abstraction at the node layer, *i.e.*, showing that the user programs with the OS model together behave as a more abstract timed model (*e.g.*, Fig. 1a). Thus we use node-local simulation, which requires reasoning about timings.

- Global Simulation by User: Finally, the user may combine all node models and the network model to obtain the refinement until a global-level specification. This layer requires global reasoning, and we can use global simulation to match two distributed system models.

# 3 Timed Behaviors of Real-Time Distributed Systems

In our formalization, we represent a distributed system as a transition system generating timed events (*i.e.*, events paired with timestamps) from each node. To address special situations triggering errors or violating timing constraints, we introduce the notions of undefined behavior (UB) and no-behavior (NB) events. Observable behaviors of a system are defined as infinite traces formed by transitions. Then, the refinement relation is straightforwardly defined as a subset relation of timed behaviors between two systems. We also explain how the framework supports imposing different assumptions using the event classification mechanism. For precise type definitions in this section, we direct readers to [Kim et al. 2024].

## 3.1 Distributed System Model

We represent a distributed system as a transition system of a triple  $(\Sigma, \to, I)$ : a set of states  $\Sigma$ , a transition relation  $\to$ , and initial states  $I \subseteq \Sigma$ . A transition  $\sigma \xrightarrow{\vec{tr}} \sigma'$  generates a distributed trace  $\vec{tr}$ , in which the i'th node-local trace  $\vec{tr}[i] = [(t_1, e_1), ..., (t_k, e_k)]$  contains events paired with timestamps that precisely denote timings. Additionally, we only consider the case  $I \neq \emptyset$ .

We represent an event as a pair  $\langle ec, r \rangle \in \text{Event}$  of an event request and a return value. <sup>3</sup> For example,  $\langle \text{read\_int}(4), 10 \rangle$  may denote an event where a program requests a 4-byte integer input and receives 10 as the return value. When events are generated from a sub-component of the model, some of them are processed by other components, while others are considered *visible*, and included in the distributed trace  $\vec{tr}$  of the transition.

<sup>&</sup>lt;sup>3</sup>In §2, we treated event requests and returns as separate events, since from the programs' perspective they occur separately in terms of timings.

*Undefined Behavior vs. No-Behavior*. Some of the visible events are designated to indicate special situations that trigger undefined behavior (UB) and no-behavior (NB) in our model by the *event classification function C*: Event  $\rightarrow$  {UB, NB, Obs} parametrized in the model, where Obs corresponds to ordinary events that form observable behaviors.

First, undefined behavior is a widely used concept that captures unexpected results that may arise from abnormal operations, *e.g.*, accessing an unallocated memory region. Therefore, it is often formally interpreted as a set of all behaviors, so that any observable behavior refines undefined behavior. It is the programmer's responsibility to avoid generating undefined behaviors in their programs. In our model, we trigger undefined behavior when the system is stuck (*i.e.*, cannot take the next step) or explicitly generates UB events.

In contrast, as a dual concept of undefined behavior, no-behavior captures improbable executions, *i.e.*, executions that violate axiomatized assumptions. NB can be interpreted as an empty set of behaviors, and thus it refines arbitrary observable behaviors. Programmers can rely on the absence of no-behavior events in reasoning about their programs, *e.g.*, considering highly-reliable time constraints as true, since no-behavior events would not happen as long as the constraints hold.

## 3.2 Timed Observable Behaviors and Refinement

For a system state  $\sigma \in \Sigma$ , we define the set of timed observable behaviors Beh $(\sigma)$  by collecting observable traces formed by infinite transition sequences starting from  $\sigma$ . Instead of revealing its coinductive definition, we state a property equivalent to the definition:

$$\overrightarrow{beh} \in \operatorname{Beh}(\sigma) \iff \operatorname{err}(\sigma) \vee (\exists \sigma', \overrightarrow{beh'}, \overrightarrow{tr}. \sigma \xrightarrow{\overrightarrow{tr}} \sigma' \wedge \operatorname{AllObs}_{C}(\overrightarrow{tr}) \wedge \\ \operatorname{concats}(\overrightarrow{tr}, \overrightarrow{beh'}) = \overrightarrow{beh} \wedge \overrightarrow{beh'} \in \operatorname{Beh}(\sigma')) \tag{1}$$

in which err is a predicate for erroneous states (*i.e.*, a state generating UB or a "stuck" state lacking any possible next step, which has the same effect as UB) whose behaviors are unpredictable, AllObs $_C$  is a predicate that holds if every event is classified as Obs by C, and concats is a pointwise concatenation of traces and behaviors. Intuitively,  $\sigma$  generates a behavior  $\overrightarrow{beh}$  if (i)  $\sigma$  is unsafe or (ii) it can make a valid transition whose trace can form  $\overrightarrow{beh}$  with one behavior of the subsequent state. From this, we define the system's behaviors  $\operatorname{Beh}(\Sigma, \to, I)$  as  $\bigcup_{\sigma \in I} \operatorname{Beh}(\sigma)$ .

Then, we can define the refinement relation of two systems as the subset relation regarding the timed observable behaviors:

Definition 3.1 (Timed Behavioral Refinement). For two distributed systems  $sys_{conc}$ ,  $sys_{abs}$  and under an event classification function C,  $sys_{conc}$  refines  $sys_{abs}$  if Beh $(sys_{conc}) \subseteq Beh(sys_{abs})$ .

**Embedding Relation of Event Classification Functions**. The event classification C can have multiple instantiations, each imposing different assumptions on the system. For example, our network model generates an event late\_delivery(m) when it fails to deliver a message m within the parameter value  $\mu$ . Users may instantiate C to classify the late delivery events as either Obs or NB. In the former, late deliveries are permitted as valid behaviors (still identifiable by the events), where the latter disallows late deliveries.

To utilize such usages regarding event classification, we define an *embedding* relation within them. Intuitively, the one that classifies more events as 0bs permits more behaviors than the one that classifies those events as NB.

Definition 3.2 (Embedding of Event Classifications). For two event classification functions  $C_1$  and  $C_2$ ,  $C_1 \leftarrow C_2$  if  $\forall e, C_1(e) = C_2(e) \lor (C_1(e) = \mathsf{Obs} \land C_2(e) = \mathsf{NB})$ .

Consequently, with a single refinement proof, users can obtain multiple verification results under different assumptions simply by substituting C. Intuitively, if a system refines a specification under a "permissive" assumption (e.g., allowing late deliveries) then the system still refines the specification under a stricter assumption (e.g., disallowing late deliveries). We show in §8 how to utilize this feature in practice. We present a theorem below that clarifies the implication of the embedding in refinement proofs.

THEOREM 3.3 (REFINEMENT PRESERVED BY EMBEDDING). For any  $C_1 \leftarrow C_2$  and  $sys_{conc}$ ,  $sys_{abs}$ , Beh $(sys_{conc}) \subseteq Beh(sys_{abs})$  under  $C_1$  implies Beh $(sys_{conc}) \subseteq Beh(sys_{abs})$  under  $C_2$ .

# 4 Concrete Formal Distributed System Model

In this section, we explain how we construct a "concrete" distributed system model that consists of the OS model, the user program for each node, and the network model. Here, we focus on how we handle the asynchrony in timings between nodes. The full details are available in [Kim et al. 2024].

## 4.1 OS Model

The OS model aims to capture the nondeterminism arising from the behavior of local clocks and asynchronous message communication. It takes as input a set of user-defined parameters that reflect the system's assumptions about local clock skew. The model then defines the semantics for a suite of system calls related to clock access and network communication, which a real-time operating system is expected to support.

**Local Clock Parameters**. In the local clock parameters, users define the type of abstract clock states and specify functions and predicates describing local clock behavior in four cases:

- LCInit(t, lc): A predicate specifying an initial clock state lc when the global time is t.

- LCVal(*lc*): A function retrieving the local time value from the current state.

- LCAdv(t, lc, lc'): A predicate for a clock state transition from t to t + 1

- LCSet(*t*, *lc*, *lt*): A function updating the clock state at *t* when the user program requests to set the local clock value to *lt*.

We present two instantiations of the parameters, which are used in the case studies in §7 and §8:

(1) Hardware clock rate assumption: This assumes a constraint on the physical clock hardware, limiting the ratio of global time to local time difference between two points (t, lt) and (t', lt') by  $\rho \in [0, 1)$ , such that:  $1 - \rho < (lt' - lt)/(t' - t) < 1 + \rho$ .

We define corresponding local clock parameters as follows:

- Clock state:  $lc = (\hat{t}, \hat{lt}, p)$  contains the global and local times at which the local clock is last set, and the "perceived" amount of time  $p \in \mathbb{R}$  since then.

- LCInit $(t, lc) \stackrel{\text{def}}{=} \exists lt. \ lc = (t, lt, 0)$

- LCVal $(lc) \stackrel{\text{def}}{=} \text{let } lc = (\_, \hat{lt}, p) \text{ in } \hat{lt} + \lfloor p \rfloor$

- LCAdv $(t, lc, lc') \stackrel{\text{def}}{=} \exists \hat{t}, \hat{l}t, p, p_{\text{inc}}.$   $1 \rho < p_{\text{inc}} < 1 + \rho \land lc = (\hat{t}, \hat{l}t, p) \land lc' = (\hat{t}, \hat{l}t, p + p_{\text{inc}})$

- LCSet $(t, lc, \hat{lt}) \stackrel{\text{def}}{=} (t, \hat{lt}, 0)$

- (2) Clock synchronization assumption: This assumption relies on the presence of a synchronization algorithm running in the background. It limits the absolute difference between global and local times by  $\varepsilon > 0$  at every point:  $|t lt| < \varepsilon$ .

The local clock parameters are defined as:

- Clock state: lc = lt, representing the current local time.

- LCInit $(t, lt) \stackrel{\text{def}}{=} |t lt| < \varepsilon$

- $LCVal(lt) \stackrel{\text{def}}{=} lt$

```

OSInit(t, (lc, skts, sts)) \stackrel{\text{def}}{=} LCInit(t, lc) \land skts = [] \land sts = Idle

\mathsf{OSLCAdv}(t,(lc,skts,sts),(lc',skts',sts')) \overset{\mathsf{def}}{=} \mathsf{LCAdv}(t,lc,lc') \land skts = skts' \land sts = sts'

OSAccept((lc, skts, sts), ms_{in}) \stackrel{\text{def}}{=} (lc, accept\_skts(skts, ms_{in}), sts)

OSCall((lc, skts, sts), f(v_1, ..., v_n)) \stackrel{\text{def}}{=} \mathbf{match} \ sts \ \mathbf{with} \ \mathsf{Idle} \Rightarrow \mathsf{Some}(lc, skts, \mathsf{Proc}(f(v_1, ..., v_n))) \mid \Rightarrow \mathsf{None} \ \mathbf{end}

OSRet((lc, skts, sts)) \stackrel{\text{def}}{=} \mathbf{match} \ sts \ \mathbf{with} \ Ret(f(v_1, ..., v_n), r) \Rightarrow Some((lc, skts, Idle), f(v_1, ..., v_n), r) \implies Some(\mathbf{n})

sc = sendto(sid, ip, port, m)) l = size(m)

sc = recvfrom(sid, sz) fetch(skts[sid]) = Some(skt', m)

skts' = skts[sid \mapsto skt'] m' = prefix(m, sz)

skts[sid] \neq \perp ms_{out} = [(ip, port, m)]

t + (lc, skts, Proc(sc)) \xrightarrow{ms_{out}} (lc, skts, Ret(sc, l))

t \vdash (lc, skts, Proc(sc)) \xrightarrow{[]} (lc, skts', Ret(sc, m'))

sc = \texttt{set\_time}(t_{l,\text{new}}) \quad lc' = \texttt{LCSet}(t, lc, t_{l,\text{new}})

sc = get time() lt = LCVal(lc)

t \vdash (lc, skts, Proc(sc)) \xrightarrow{[]} (lc, skts, Ret(sc, lt))

t \vdash (lc, skts, Proc(sc)) [], (lc', skts, Ret(sc, 0))

sc = sleep(lt_w) lt_s = LCVal(lc)

lt = LCVal(lc) lt < lt_s + lt_w

sc = sleep(lt_w) lt = LCVal(lc) lt_s + lt_w \le lt

t \vdash (lc, skts, Proc(sc))

t \vdash (lc, skts, Wait(lt_s, lt_w)) \xrightarrow{[]}

t \vdash (lc, skts, Wait(lt_s, lt_w)) \xrightarrow{[]}

(lc, skts, Wait(lt_s, lt_w))

(lc, skts, Wait(lt_s, lt_w))

(lc, skts, Ret(sc, 0))

```

Fig. 5. Selected OS-model transition rules

• LCAdv $(t, lt, lt') \stackrel{\text{def}}{=} lt \le lt' \land (|t - lt| < \varepsilon \implies |(t + 1) - lt'| < \varepsilon)$ • LCSet $(t, lt, lt_{\text{new}}) \stackrel{\text{def}}{=} lt_{\text{new}}$

Note that the second intantiation maintains the skew between the local and global clocks within the given bound, provided the system does not set the clock. When the system does set the clock, we consider two scenarios: (i) if the new time still falls within the clock skew bound, the model continues to behave normally, and (ii) if the new time exceeds the clock skew bound, the local clock will be updated to an arbitrary value in a nondeterministic manner, which prevents any proof from proceeding successfully. In essence, when setting the clock, we must prove that the new time does not violate the clock skew bound. This approach ensures that our proofs remain valid only when clock adjustments stay within the specified boundaries.

**Building OS Model with System Calls.** We now define the OS model based on the local clock parameters as follows. An abstract OS state os = (lc, skts, sts) consists of a clock state, a set of open sockets, and a status indicating the ongoing process. Sockets can be bound to a port number, and store inbound messages in their buffers. A status is either:

- Idle: No ongoing process

- Proc(sc): Processing a system call sc with arguments (e.g., sc = sleep(10))

- Wait( $lt_s, lt_w$ ): OS started waiting for  $lt_w$  amount of time since  $lt_s$  (in terms of local time)

- Ret(sc, v): Returing from sc with value v

Fig. 5 presents the functions and predicates that define the OS model's event handling. These events include initialization, local clock advancement, network message reception, and the invocation, processing, and return of system calls. The OSInit predicate defines valid initial states of the OS, while OSLCAdv advances the local clock in accordance with LCAdv. When messages are received from the network, the OSAccept function distributes them to the appropriate open sockets. System call invocations are handled by OSCall, which changes the status from Idle to Proc. Once processing is complete, OSRet returns control and the resulting value to the program. For system call processing, the rules follow the form  $t \vdash os \xrightarrow{m_{\text{Sout}}} os'$  describing how the processing changes the state of the OS with any messages transmitted to the network  $(ms_{\text{out}})$  at one time unit. Throughout the paper, we use the shorthand notation  $t \vdash s \xrightarrow{e} s'$  for  $(t, s) \xrightarrow{e} (t + 1, s')$ . The bottom of Fig. 5 presents specific rules for selected system calls.

```

t \vdash st \xrightarrow{(ms_{in}, te, ms_{out})} st'

(LATENCY)

(INITIALIZE)

(Failure)

(TimeViolation)

OSInit(os) ProgInit(s)

st = (tr, lat, to, os, s) LCVal(os) < to lat > 0

st = (tr, lat, to, os, s)

st = (tr, lat, \infty, os, s)

st = (tr, lat, to, os, s)

OSAccept(os, ms_{in}) = os_1 st' = (tr, lat - 1, to, os_1, s)

LCVal(os) \ge to

t \vdash (tr, \mathsf{Off}) \xrightarrow{(ms_{in}, \tau, [])} st \ t \vdash st \xrightarrow{(ms_{in}, \tau, [])} (tr, \mathsf{Off})

t \vdash st = \frac{(ms_{in}, \tau, [])}{st'}

t \vdash st = (ms_{in}, \tau, []), st

\begin{aligned} st &= (tr, 0, to, os, s) \quad lt = \text{LCVal}(os) < to \quad \text{OSAccept}(os, ms_{\text{in}}) = os_1 \quad t \vdash (os_1, s) \xrightarrow{(e.ms_{\text{out}})} (os_2, s') \quad \text{OSLCAdv}(t, os_2, os') \\ tr' &= \text{app\_last}(tr, lt, e) \quad to' &= \mathcal{T}(tr, lt, e, to) \quad te = ((\text{isObsEv}(e)))? (\text{TimeOf}(lt), e) : \tau) \quad st' &= (tr', lat, to', os', s') \end{aligned}

t \vdash st \xrightarrow{(ms_{in}, te, ms_{out})} st'

t \vdash (os_1, s) \xrightarrow{(e, ms_{out})} (os_2, s')

(PROGRAMSTEP)

(OSSTEP)

(OSRETURN)

(OSCALL)

s \xrightarrow{\tau^*} s_1 \xrightarrow{e} s' \quad e = f(v_1, ..., v_n)

sc = f(v_1, ..., v_n)

s \xrightarrow{\tau}^* s_1 \xrightarrow{e} s'

OSRet(os_1) = Some(os_2, sc, r)

isIdle(os_1)

isOScall(s', e)

s \xrightarrow{\langle sc,r \rangle} s'

\negisOScall(s', e)

OSCall(os_1, e) = Some(os_2)

t \vdash os_1 \xrightarrow{ms_{\text{out}}} os_2

t \vdash (os_1, s) \xrightarrow{(e, [])} (os_1, s')

t \vdash (os_1, s) \xrightarrow{(e, [])} (os_2, s')

t \vdash (os_1, s) \xrightarrow{(\langle sc, r \rangle, [])} (os_2, s')

t \vdash (os_1, s) \xrightarrow{(\tau, ms_{out})} (os_2, s')

Fig. 6. Node transition rules

```

#### 4.2 Concrete Node Model

Now, we construct a concrete node model by integrating the OS model with the untimed semantics of a program. Building upon the timed operational semantics construction method described in §2, we address additional complexities, including node failures, local clocks, message communication through the network, and control transitions between the program and OS. Fig. 6 presents the transition rules for this model, which we will explain in detail.

To model node failures, we define a node state as either inactive (tr, 0ff) or active (tr, lat, to, os, s), with the active state following our construction method. An inactive node may reboot at any time, as described by the Initialize rule. We assume a predicate ProgInit specifies the program's initial states. Conversely, an active node may unexpectedly fail, as described by Failure.

The next three rules largely follow our construction method, with adaptations for local clock and message communication. In these rules, we compare the timeout to against LCVal(os), implicitly coercing os to its clock state. For message communication, non-violation transitions (LATENCY and Progress) first process incoming messages  $ms_{\rm in}$  via OSAccept. Latency simply decreases lat thereafter. Progress involves a nested transition for OS and program state, followed by local clock advancement via OSLCAdv. To determine the timed observable event te, we exclude non-observable events like  $\tau$  and system call events, which are considered internal program-OS communication. The framework takes as input a timestamp generator TimeOf, supporting timestamp abstraction. This feature is used in §8 for matching timestamps between asynchronous and synchronous executions. System call events are still recorded in tr, as  $\mathcal T$  uses them to update to.

The bottom four rules in Fig. 6 present the transitions of program and OS states, and how control passes between them. ProgramStep and OSStep represent normal transitions of the program and OS components, respectively. Program steps can occur when the OS is idle, while OS steps may involve releasing outgoing messages, as we have seen in §4.1. We define a predicate isOScall to determine if a program state has just called a specific system call. OSCALL and OSRETURN represent the control transfers between the program and OS, potentially updating timeout values.

## 4.3 Network Model

The top-level structure of the concrete distributed system model is composed of a list of node models and our network model. A node model is a tuple  $(ip, ST, \rightarrow, st_{init})$  of the node's distinct IP address ip, set of states ST, transition rules  $\rightarrow$ , and initial state  $st_{init}$ . Our concrete node model is an instance of node model, with  $st_{init} = \{([], 0ff)\}$ . The network model is a transition system with

two separate transition stages for distributing ( $\rightarrow_{\text{distr}}$ ) and gathering ( $\rightarrow_{\text{gather}}$ ) messages generated from the nodes. The network model can represent various types of network behaviors by setting two parameters: the maximum delivery time  $\mu$  and the maximum duplicated deliveries  $\kappa$  for a message. If the network takes a transition step violating the parameters, it generates a special event that can later be classified as no-behavior by the event classification C. We present the construction of a distributed system model  $(\Sigma, \rightarrow, I)$  in §3 as follows.

A global state  $(t, nw, \vec{st})$  consists of a global time, a network state, and a list of node states. First, a network state is a pair  $nw = (\vec{mc}, \vec{ms})$  of a multicast group table and a list of in-transit messages. Each entry  $(ip_{\text{mc}}, ip, t_{\text{send}}, b) \in \vec{mc}$  contains the IP address of a multicast group (e.g., one of Class D addresses [Cotton and Vegoda 2010]), the local IP address of a node belonging to the group, the time the "join" request is released to the network, and the boolean flag indicating whether the join process is completed (which also takes at most  $\mu$  since it is requested). Each entry  $(ip_{\text{dst}}, m, t_{\text{send}}, d) \in \vec{ms}$  contains a message, the time it was released to the network, and the number of deliveries (>1 for duplicates) until now. Third, each entry  $\vec{st}[i]$  represents the current state of the i'th node. The initial global state is given by  $(0, ([], []), [st_{\text{init},0}, \dots, st_{\text{init},N-1}])$ , for N nodes.

The transition rule of a global state is given as follows:

$$\underbrace{t \vdash nw \xrightarrow{(\vec{ms}_{\text{in}}, te_{\text{nw}})}_{\text{distr}} nw_1 \quad \forall i < N. \ t \vdash \vec{st} [i] \xrightarrow{(\vec{ms}_{\text{in}}[i], \vec{te}[i], \vec{ms}_{\text{out}}[i])} \vec{st}' [i] \quad t \vdash nw_1 \xrightarrow{\vec{ms}_{\text{out}}}_{\text{gather}} nw'}_{\text{gather}} (t, nw, \vec{st}) \xrightarrow{te_{\text{nw}} :: \vec{te}}_{\text{nw}} (t + 1, nw', \vec{st}')}$$

Note that a transition occurs at every tick of the time unit in three stages:

- **Distributing Messages:** The distributing network transition  $\rightarrow_{\text{distr}}$  non-deterministically selects the messages  $\vec{ms}_{\text{in}}$  to be distributed in this step and updates the multicast group table, resulting in the intermediate network state  $nw_1$ . Here,  $\vec{ms}_{\text{in}}$  is an indexed list according to the IP addresses of the nodes.  $te_{\text{nw}}$  may contain three kinds of network events related to  $\mu$  and  $\kappa$ : (i) LateDeliv( $ip_{\text{dst}}, m$ ) if  $\mu$  has just expired now but m is not delivered yet, (ii) DupOverLimit( $ip_{\text{dst}}, m$ ) if m has already been delivered at least  $\kappa$  times but is included again in  $\vec{ms}_{\text{in}}$ , and (iii) LateArrv( $ip_{\text{dst}}, m$ ) if  $\mu$  has already expired but m is included in  $\vec{ms}_{\text{in}}$ .

- Taking a Step: With the incoming messages, each node takes a step in parallel. Each node state  $\vec{st}[i]$  at time t takes the incoming messages  $\vec{ms}_{in}[i]$ , generates timed events  $\vec{te}[i]$  and a (possibly empty) outgoing message  $\vec{ms}_{out}[i]$ , and transitions to the next state  $\vec{st}'[i]$  at time t+1.

- Gathering Messages: After every node takes a step, the network gathers the outgoing messages  $\vec{ms}_{\text{out}}$  to form the next network state nw'. Specifically, this step adds entries of  $\vec{mc}$  or  $\vec{ms}$  for each well-formed outgoing message according to the message type: either a normal data message or a multicast join request. For example, if a message contains normal data sent to a multicast group, the message is copied for each group member according to  $\vec{mc}$  and then included in  $\vec{ms}$ .

# 5 Proof Techniques

VERIRT offers three simulation relations as proof techniques to assist the user in proving the refinement. Each technique is designed for different stages in the end-to-end refinement proof outlined in Fig. 4. From the bottom of the figure, we will discuss how each proof technique addresses the challenges at each stage. For the presentation purpose, we omit stuttering indexes [Leroy 2009b] from our simulation relations in this section, which is indeed necessary for their soundness.

Note that, the three simulation relations we present here, each matching *states* of two semantics at each level, can be easily lifted to relations matching two *semantics* themselves. Hence, when referring to simulation, we interchangeably use the term for both between states and semantics.

# 5.1 Program-Local Simulation

The program-local simulation relation is used for local abstractions on the program components in the concrete distributed system model, which occurs in the first two stages of the end-to-end refinement proof. In the first stage, the framework internally applies this technique to construct the formal compiler correctness proof with respect to the global-level timed behaviors (see §6). In the second stage, the user is expected to verify their C programs against their abstract specifications, which will ensure the absence of implementation bugs and also facilitate subsequent refinement proofs by preemptively abstracting away the subtleties of formal C semantics.

For this purpose, we design our program-local simulation as a conventional, untimed simulation relation. This is made possible by the fact that our composition of timed operational semantics from the computational behaviors and timing assumptions is essentially orthogonal. Once the user establishes a program-local simulation proof, the framework will internally lift it to a node-local simulation (§5.2) by combining it with the given timing assumptions.

The definition of the simulation relation between two "source" and "target" program semantics  $(S_s, \rightarrow_s, I_s, F_s)$  and  $(S_t, \rightarrow_t, I_t, F_t)$  is like the following:

$$s_{s} \gtrsim s_{t} \stackrel{\text{coind}}{=} (i) \ (s_{s} \in F_{s} \land s_{t} \in F_{t}) \lor (ii) \ \text{err}(s_{s}) \lor$$

$$(iii) \ \neg \text{err}(s_{t}) \land (\forall e, s'_{t}. \ s_{t} \stackrel{e}{\to} s'_{t} \Rightarrow \exists s'_{s}. \ s_{s} \stackrel{e}{\to} + s'_{s} \land s'_{s} \gtrsim s'_{t})$$

$$(2)$$

The relation coinductively matches two program states  $s_s$  and  $s_t$  as follows. First, two states are matched if they are (*i*) final states, (*ii*) if  $s_s$  may trigger undefined behavior (denoted as err( $s_s$ )), or (*iii*)  $s_t$  is a safe (*i.e.*, non UB-generating) state where every step from it can be matched with one or more steps of  $s_s$ .

## 5.2 Node-Local Simulation

After the abstraction of programs, the user may use our node-local simulation relation for further local abstractions on the OS-Node models. Specifically, the user is supposed to show that the compositions of the timing assumptions and the computational specifications of programs together refine more abstract node-level specifications (*e.g.*, Fig. 1).

Now, we need to build a *timed simulation*, *i.e.*, one can simulate another in terms of not only the order of events, but also the timings, too. In particular, the incoming and outgoing messages should occur at exactly identical times, since the incoming messages are controlled by the environment (*i.e.*, the network model) and differences in timings of outgoing messages may alter the behaviors of other nodes.

Therefore, the user is required to resolve node-local timing issues throughout the proof. Especially, the OS-Node model may produce an infinite number of non-deterministic timed behaviors due to the random latencies of internal program steps and skews of the local clock. The main task of the proof is thus to make sure that the non-determinism in timings is well-constrained by no-behavior events generated according to the given time constraints.

To assist the proof from the framework's side, we design the node-local simulation as follows, where the key differences with conventional simulations are highlighted in red:

$$t \vdash st_{s} \gtrsim st_{t} \stackrel{\text{coind}}{=} \operatorname{err}(st_{s}) \lor \\ \neg \operatorname{err}(st_{t}) \land (\forall ms_{\text{in}}, te, ms_{\text{out}}, st'_{t}. (t \vdash st_{t} \xrightarrow{(ms_{\text{in}}, te, ms_{\text{out}})} st'_{t}) \Rightarrow \\ (i) \exists t_{N}, e_{N}. (t_{N}, e_{N}) \in te \land C(e_{N}) = \text{NB} \lor \\ (ii) \exists st'_{s}. (t \vdash st_{s} \xrightarrow{(ms_{\text{in}}, te, ms_{\text{out}})} st'_{s}) \land ((t+1) \vdash st'_{s} \gtrsim st'_{t}))$$

$$(3)$$

The differences are introduced for the following reasons. First, the relation takes the global time t since the transition rules of a node-level operational semantics may depend on t. Second, for a target step generating NB events, the simulation does not require matched source steps, since the target step will not produce any observable behaviors. Third, for each target step it requires exactly one matched source step to enforce the events and message exchanges to occur at the identical time. Recall that a single OS-Node step takes one time tick, during which an arbitrary number of program steps may take place to account for the non-determinism of timings.

We present our simulation-lifting theorem that converts a program-local simulation into a node-local simulation between two OS-Node states here (see [Kim et al. 2024] for the proof sketch):

```

Theorem 5.1 (Simulation-Lifting Theorem). For two programs p_s, p_t, \forall s_s \in p_s.S, s_t \in p_t.S. s_s \gtrsim s_t \implies \forall t, tr, lat, to, os. t \vdash (tr, lat, to, os, s_s) \gtrapprox (tr, lat, to, os, s_t).

```

#### 5.3 Global Simulation

Finally, the framework provides the global simulation relation for abstractions of the entire system. With this simulation, the user can complete the end-to-end refinement from the distributed system model with assembly programs to a monolithic, centralized abstract specification of the system. The user would aim to abstract away subtleties caused by distributed computation, *e.g.*, randomness in network message delivery times and asynchronous paces of execution between the nodes.

Eliminating the asynchronies may require the reallocation of events over multiple steps. For example, consider the top-level global specification as an ideally synchronized model in which every node periodically runs in a lock-step manner. In this case, events for a certain period will be generated at a designated time, simultaneously. However, the corresponding concrete distributed system model will generate events with certain intervals between them, asynchronously between the nodes, reflecting the real-world scenario. Therefore, a proof technique that supports event reallocation over multiple steps would be helpful in this stage.

For this purpose, we designed our global simulation as a *delayed simulation* below, which allows one to postpone the decision of matched source steps during the proof by accumulating the trace generated by multiple target steps:

$$\sigma_{s} \underset{tr_{acc}}{\approx} \sigma_{t} \overset{\text{coind}}{=} \operatorname{err}(\sigma_{s}) \vee \\

\neg \operatorname{err}(\sigma_{t}) \wedge (\forall \vec{te}_{t}, \sigma'_{t}. (\sigma_{t} \xrightarrow{\vec{te}_{t}} \sigma'_{t}) \Rightarrow \\

(i) \exists t_{N}, e_{N}. (t_{N}, e_{N}) \in \vec{te}_{t} \wedge C(e_{N}) = NB \vee (ii) \sigma_{s} \underset{\approx}{\approx}_{(tr_{acc} + \vec{te}_{t})} \sigma'_{t} \vee \\

(iii) \exists \vec{te}_{s}, \sigma'_{s}. \sigma_{s} \xrightarrow{\vec{te}_{s}} \sigma'_{s} \wedge \vec{te}_{s} \equiv (tr_{acc} + + \vec{te}_{t}) \wedge (\sigma'_{s} \underset{\approx}{\approx}_{1} \sigma'_{t}) \tag{4}$$

Now, the relation is indexed with a trace  $tr_{\rm acc}$ . The main difference is that when the target state  $\sigma_{\rm t}$  takes a step, the user may choose to accumulate the trace (ii) to delay the matching process. After that, when the target system reaches a proper state (iii), the user gets to pick proper source steps that generate an equivalent trace to resolve the accumulated trace and can proceed to the next relation with the empty trace index. The equivalence relation  $\equiv$  decides whether the two traces have timed events with identical order and timestamps but without requiring them to be generated in identical time ticks.

## 6 Lifting CompCert's Proof

The bottom-most stage in the end-to-end refinement is a composition of two sub-stages of proof included in CompCertRT. First, we generically convert the CompCertM [Song et al. 2019]'s "mixed-simulation" to our timed program-local simulation, from which we derive the timed refinement

using Theorem 5.1. Up to this point, the assembly modules are logically linked by CompCertM's module semantics. Then, by porting CompCertM's proof of the adequacy of logical linking of assemblies against syntactic linking, we complete the end-to-end timed refinement proof with respect to the syntactic linking of compiled assemblies.

## 6.1 Lifting of Mixed Simulation

First, We derive our program simulation from the mixed simulation of CompCertM. Let  $\mathcal{R}$  be the set of mixed simulations—a few instantiations of a single generic open simulation—used by CompCertM that covers every compiler pass of CompCert. See [Kim et al. 2024] for the properties of mixed simulation.

LEMMA 6.1 (MIXED SIMULATION TO PROGRAM SIMULATION). For any pair of modules  $(M_S, M_T)$  related by a mixed simulation relation  $R \in \mathcal{R}$ , and any two list of modules  $\vec{M}_L$  and  $\vec{M}_R$  whose element is self-related by R (i.e.,  $\forall M \in \vec{M}_L \cup \vec{M}_R.(M,M) \in R$ ), the following program-local simulation holds:  $(\vec{M}_L + + [M_S] + + \vec{M}_R) \gtrsim (\vec{M}_L + + [M_T] + + \vec{M}_R)$ .

By applying Lemma 6.1 and Theorem 5.1 repeatedly, we prove Lemma 6.2 that guarantees the correctness of the CompCertM's translation C w.r.t. timed refinement.

LEMMA 6.2 (CORRECTNESS OF COMPCERTM'S TRANSLATION). For any list of Clight modules  $[S_1,...,S_n]$  and Asm modules  $[T_1,...,T_n]$ , if  $C(S_i)=T_i$  for each  $i \in [1,n]$ , then for any identical ip, the concrete node model with the program  $[T_1,...,T_n]$  contextually refines the concrete node model with the program  $[S_1,...,S_n]$ .

# 6.2 Syntactic Linking of Assembly Programs

While the result of Lemma 6.2 lowers each Clight module into the compiled Asm modules, the modules are logically linked by the interaction semantics. We first prove Lemma 6.3 that implies that the syntactic linking of the Asm modules preserves the semantics, and combine it with Lemma 6.2 to prove the final compiler correctness theorem in terms of the concrete system model.

LEMMA 6.3 (SYNTACTIC LINKING OF ASMS). For any list of Asm modules  $[T_1, ..., T_n]$ , if the syntactic linking succeeds and produces an Asm module T such that  $T_1 \circ ... \circ T_n = T$ , then  $[T_1, ..., T_n] \gtrsim [T]$ .

Theorem 6.4 (Lifting CompCert's Proof). For a C program  $C^i = [S^i_1, ..., S^i_n]$  consisting of multiple C files and the assembly program  $A^i = [T^i]$  obtained by syntactically linking the separately compiled assemblies for each i, the concrete distributed system model with  $[A^1, ..., A^n]$  refines the concrete distributed system model with  $[C^1, ..., C^n]$ .

# 7 Case Study 1: Clock Synchronization

Cristian's algorithm is a protocol for synchronizing local clocks in distributed systems using a client-server architecture [Cristian 1989]. The algorithm's simple structure involves one round-trip message exchange between a client and server. The process begins with the client requesting the server's local clock value. Upon receiving the response, the client adjusts its local clock based on the assumption that the travel times for the request and response messages are likely to be similar. In this case study, we develop and verify a client-server system that periodically synchronizes local clocks using Cristian's algorithm.

# 7.1 Analysis on Clock Synchronization

We conduct a formal analysis of the bounds of clock skews based on these assumptions:

- Hardware clock skew: The local clocks follow the hardware clock rate assumption (§4.1).

- System call response delay: When the program is waiting for a certain condition via a system call (e.g., a response from the timer or the network), the execution will resume within a constant time  $\delta$  in terms of the local clock, after the condition is satisfied.

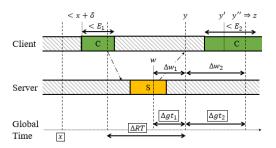

Fig. 7. Analysis of Cristian's algorithm

- WCET (Bounded execution time for sending a request): The local time between a timer return and waiting for the server's response is bounded by  $E_1$  (see Fig. 7).

- WCET (Bounded execution time for processing the response): After the client receives the response, the local time until the client's local clock is updated is bounded by  $E_2$ .

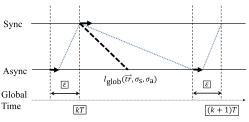

Now, we walk through one successful period of synchronization illustrated in Fig. 7. Consider a period that is supposed to start at x. When the period starts, the timer wakes up the client before its local clock points  $x + \delta$  and the round trip of messages begins within  $E_1$ . Within the round trip that takes  $\Delta RT$ , the server receives the request and sends the response message that contains a local time w sampled in between. Let  $\Delta t_1$  denote the global time taken from the sampling of w to the end of the round trip, during which the local clocks of the client and server change to y and  $w + \Delta w_1$ . Then, within  $\delta$ , the client will resume, so reads its local time y' and then sets the local clock from a value y'' to z = w + (y' - x)/2 within  $E_2$  after the resume. Let  $\Delta t_2$  denote the global time taken from the end of the round trip up to this point, during which the local clocks of the server change to  $v = w + \Delta w_1 + \Delta w_2$ .

We derive the following bound, which depends on  $\Delta RT$  (see [Kim et al. 2024] for details):

$$-(\frac{1+3\rho}{2})\Delta RT - \frac{1+\rho}{1-\rho}(\delta + E_2) \le z - v \le \frac{1+\rho}{2}\Delta RT + \frac{1}{2}(\delta + E_1)$$

Building on this result, we can bound the skew by imposing additional assumptions on the network and the server-side execution time. Let us assume that the message delivery time is bounded by  $\mu$ , and the server-side operation takes at most  $\delta + E_3$ . Then, we obtain  $\Delta RT \leq 2\mu + E_3/(1-\rho)$ , resulting in the following skew bound  $\varepsilon$ :

$$|z-v| < \varepsilon = \max\left(\left(\frac{1+3\rho}{2}\right)(2\mu + E_3/(1-\rho)) + \frac{1+\rho}{1-\rho}(\delta + E_2), \frac{1+\rho}{2}(2\mu + E_3/(1-\rho)) + \frac{1}{2}(\delta + E_1)\right)$$

*Our System Design.* In practical implementations of the above algorithm, server-side queues of pending requests can complicate verification. These queues may form due to various factors: overly frequent or duplicate client requests, delayed message deliveries, competition among multiple clients, and other issues. Since an unpredictable number of pending requests can prevent accurate estimation of an upper bound for  $\Delta RT$ , we need to establish conditions to control these factors to eliminate pending requests.

To address the issue, we configure our network model as  $\kappa=1$ , setting  $C(\texttt{LateDeliv}(\_,\_))=0$ bs while classifying other network events as NB. This configuration eliminates message duplication and late arrivals, while permitting message drops. Such a setup can be realized through a background procedure that runs a duplicate resolution algorithm and discards excessively delayed messages by examining their timestamps.

For simplicity, we narrow our focus to a single-client scenario. We program the client to maintain a minimum interval  $E_{\text{wait}}$  between successive requests. Specifically, this interval must satisfy the condition:  $\mu + (\delta + E_3)/(1-\rho) < E_{\text{wait}}/(1+\rho)$ . Here,  $(\delta + E_3)/(1-\rho)$  represents the maximum global time for the server to process a request, while  $E_{\text{wait}}/(1+\rho)$  is the minimum global time for the client to wait  $E_{\text{wait}}$  with respect to its local clock.

#### 7.2 Verification

To verify the skew bound presented in  $\S7.1$  for our implementation, we design a specification and proof structure based on two abstract node models. We define two such models, one for the server and one for the client, each with its own local clock. For each abstract node, we establish a node-local simulation with its corresponding concrete node, which also ensures exact matching of local clocks. We then prove that the distributed system with these abstract nodes satisfies a global invariant  $I_{\text{glob}}$ , from which we derive the skew bound. By combining these results with the soundness of node-local simulation provided by VeriRT, we prove our goal.

*Handling Distributed Concurrency.* For a system state  $(t, nw, [st_{sv}, st_{cl}])$  where  $st_{sv}$  and  $st_{cl}$  represent the abstract server and client node states respectively, we define local invariants for each node to facilitate local reasoning. Our proof proceeds in three steps: we derive the local invariants from the global invariant, verify their preservation during transition steps, and then combine these results to establish the global invariant for the subsequent state. We focus here on the server-side local invariant; the client-side follows a similar approach, which is detailed in [Kim et al. 2024].

The server-side local invariant consists of two parts:  $I_{sv}(t, nw, st_{sv}) = I_{sv}^{st}(t, nw, st_{sv}) \wedge I_{sv}^{rsp}(t, nw, st_{sv})$ . At a high level,  $I_{sv}^{st}$  implies:

- (1) If  $st_{sv}$  is idle, nw contains at most one in-transit request from the client.

- (2) If  $st_{sv}$  is processing a request  $req = \langle id_{req} \rangle$ , then nw contains no in-transit requests. For such req, let  $t_s^{req}$  and  $t_r^{req}$  be the client's sending time and server's receiving time, respectively. Then  $t_r^{req} t_s^{req} < \mu$  and  $t t_r^{req} < (\delta + E_3)/(1 \rho)$ .

$I_{\rm sv}^{\rm rsp}$  implies that for any in-transit response  $rsp = \langle id_{\rm req}, t_{\rm sv} \rangle$  in nw, there exists a corresponding request  $req = \langle id_{\rm req} \rangle$  in nw satisfying the following: let  $t_{\rm s}^{req}$  and  $t_{\rm r}^{req}$  be req's sending and receiving times, and  $t_{\rm s}^{rsp}$  be rsp's sending time, then  $t_{\rm r}^{req} - t_{\rm s}^{req} < \mu$ ,  $t_{\rm s}^{rsp} - t_{\rm r}^{req} < (\delta + E_3)/(1-\rho)$ , and  $t - t_{\rm s}^{rsp} < \mu$ . Additionally,  $t_{\rm sv}$  must be a valid local time sampled by the server between  $t_{\rm r}^{req}$  and  $t_{\rm s}^{rsp}$ .

For message generation, we assume a property of client-generated messages that must be proven on the client side:  $G_{\rm cl}(t,nw,ms_{\rm out,cl}) = \forall req' \in ms_{\rm out,cl}, req \in nw.\ req' \neq req \land t_{\rm s}^{req} + E_{\rm wait}/(1+\rho) < t$ . This ensures the client adheres to the minimum interval  $E_{\rm wait}$ . Conversely, the server must guarantee a property for the client side:  $G_{\rm sv}(t,nw,ms_{\rm out,sv}) = \forall rsp = \langle id_{\rm req},t_{\rm sv}\rangle \in ms_{\rm out,sv}.\ \langle id_{\rm req}\rangle \in nw$ .

Lemma 7.1, which states the preservation of  $I_{sv}$ , is presented below along with a high-level proof:

Lemma 7.1 (Server-side local invariant). For a global state  $(t, nw, [st_{sv}, st_{cl}])$ , a distribution of messages  $t \vdash nw \xrightarrow{([ms_{in,sv}, ms_{in,cl}], te_{nw})} distr} nw_1$  with no NB events in  $te_{nw}$  and a node-local transition  $t \vdash st_{sv} \xrightarrow{(ms_{in,sv}, te_{sv}, ms_{out,sv})} st'_{sv}$ , if  $I_{sv}(t, nw, st_{sv})$  and  $G_{cl}(t, nw, ms_{out,cl})$  hold, then  $G_{sv}(t, nw, ms_{out,sv})$  holds, and for the network gathering step  $t \vdash nw_1 \xrightarrow{[ms_{out,sv}, ms_{out,cl}]} gather nw'$ ,  $I_{sv}(t + 1, nw', st'_{sv})$  holds.

PROOF. We perform a case analysis on  $st_{sv}$  as follows:

- If  $st_{sv}$  is idle: nw' will have at most one request. If there is a new request in  $ms_{out,cl}$ ,  $G_{cl}$  ensures  $t_s^{req} + \mu < t$  for all existing req, implying req is not in-transit.

- If no request arrives:  $st'_{sv}$  remains idle, implying  $I_{sv}^{st}$ .  $I_{sv}^{rsp}$  holds as there is no new response in nw' and remaining in-transit responses satisfy the conditions.

- If a new request req arrives: The server processes req, establishing  $I_{sv}^{st}$  from the network assumptions.  $I_{sv}^{rsp}$  holds for the same reason as above.

- If  $st_{sv}$  is processing a request req:  $G_{cl}$  and  $I_{sv}^{st}$  together imply  $ms_{out,cl} = []$ . If  $st_{sv}'$  still processes req:  $I_{sv}^{st}$  holds, otherwise  $t t_{r}^{req} \ge (\delta + E_3)/(1 \rho)$  contradicts the timing assumptions.

- \* If  $ms_{out.sv}$  is empty:  $I_{sv}^{rsp}$  holds as in previous cases.

- \* If  $ms_{out,sv}$  contains rsp: rsp is a new response for req.  $I_{sv}^{rsp}$  holds for the new response.  $G_{\rm sv}$  is ensured straightforwardly with req.

- If  $st'_{sv}$  completes processing  $req: I_{sv}^{st}$  holds as  $st'_{sv}$  is idle with no in-transit request.  $I_{sv}^{rsp}$  holds under the same case analysis on msout.sv.

Finally, we define the global invariant as  $I_{\text{glob}}(t, nw, [st_{\text{sv}}, st_{\text{cl}}]) = I_{\text{sv}}(t, nw, st_{\text{sv}}) \land I_{\text{cl}}(t, nw, st_{\text{cl}})$ . From the lemmas on local invariants, we derive Theorem 7.2, which establishes the preservation of the global invariant.

Theorem 7.2 (Global invariant). For a global state  $(t, nw, [st_{sv}, st_{cl}])$  that satisfies the invariant  $I_{\text{glob}}(t, nw, [st_{\text{sv}}, st_{\text{cl}}]), \text{ any transition step } (t, nw, [st_{\text{sv}}, st_{\text{cl}}]) \xrightarrow{\vec{tr}} (t', nw', [st'_{\text{sv}}, st'_{\text{cl}}]) \text{ without generat-}$ ing NB satisfies  $I_{glob}(t', nw', [st'_{sv}, st'_{cl}])$ .

# Case Study 2: PALSware

PALSware [Al-Nayeem et al. 2013] is a middleware implementation of physically asynchronous logically synchronous (PALS) architectural design [Al-Nayeem et al. 2009; Sha et al. 2009] for realtime distributed systems. It aims to provide a logically synchronous view for the application layer on top of an asynchronous underlying environment based on a set of assumptions. An application of PALSware consists of multiple modules, called tasks, that run on each physical node. Each physical node runs a PALSware instance, which periodically launches its task's job.

## Correctness of Synchronization